К1801ВП1-35: различия между версиями

Panther (обсуждение | вклад) Нет описания правки |

Xolod (обсуждение | вклад) |

||

| (не показаны 2 промежуточные версии 1 участника) | |||

| Строка 146: | Строка 146: | ||

|- | |- | ||

|30 | |30 | ||

| | |NP | ||

|Вход установки паритета | |Вход установки паритета | ||

|- | |- | ||

| Строка 343: | Строка 343: | ||

|заглавие = Базовые матричные кристаллы и матричные БИС | |заглавие = Базовые матричные кристаллы и матричные БИС | ||

|оригинал = | |оригинал = | ||

|ссылка = | |ссылка = https://emuverse.ru/downloads/books/BMK_1992.pdf | ||

|ответственный = | |ответственный = | ||

|издание = | |издание = | ||

| Строка 357: | Строка 357: | ||

}} | }} | ||

* {{книга | * {{книга | ||

|автор = Н. Н. Аверьянов и др. /Под ред. В. А. Шахнова | |автор = Н. Н. Аверьянов и др. / Под ред. В. А. Шахнова. | ||

|часть = | |часть = | ||

|заглавие = Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2-х т. | |заглавие = Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2-х т. | ||

|оригинал = | |оригинал = | ||

|ссылка = | |ссылка = https://emuverse.ru/downloads/books/Shakhnov_MPK_1988_Vol_2.djv | ||

|ответственный = | |ответственный = | ||

|издание = | |издание = | ||

| Строка 367: | Строка 367: | ||

|издательство = Радио и связь | |издательство = Радио и связь | ||

|год = 1988 | |год = 1988 | ||

|том = | |том = 2 | ||

|страницы = | |страницы = | ||

|страниц = | |страниц = | ||

Текущая версия от 22:16, 18 сентября 2023

Устройство интерфейса с последовательной передачей данных (ИРПС) на К1801ВП1-035

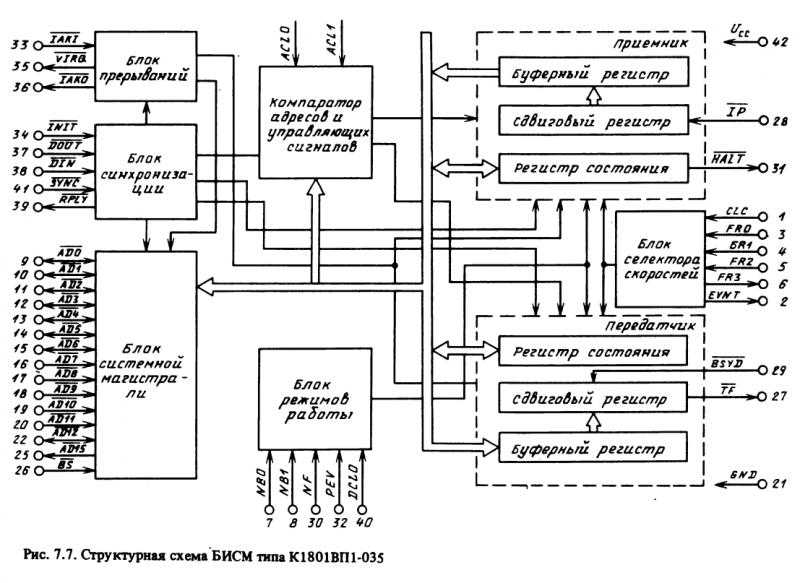

Рассмотрим вопрос реализации ИРПС. В составе ЭВМ для связи процессора с удаленным устройством, в частности с пультовым терминалом, используется последовательная передача данных. Для преобразования параллельной информации в последовательную и наоборот при подключении к микроЭВМ «Электроника-60» периферийных устройств через ИРПС предназначена микросхема К1801ВП1-035.

Структурная схема БИС К1801ВП1-035 приведена на рис. 7.7, обозначение и наименование выводов даны в табл. 7.5. Начальная установка микросхемы производится подачей сигналов низкого уровня на входы INIT и DCLO.

|

|

Микросхема К1801ВП1-035 содержит четыре регистра и два источника адресов векторов прерывания. Адреса регистров и векторов объединены в четыре группы, которые указаны в табл. 7.6. Выбор групп адресов регистров и источников адресов векторов прерываний производится заданием комбинаций уровней на входах ACL0 и АСL1 соответственно: для группы 1 – 0 и 0, для группы 2 – 1 и 0, для группы 3 – 0 и 1, для группы 4 – 1 и 1.

Выбор форматов посылок по последовательному каналу производится заданием комбинаций уровней на входах NB0 и NB1 соответственно: для 8 бит – 1 и 1, для 7 бит – 0 и 1, для 5 бит – 0 (либо 1) и 0.

Скорость обмена по последовательному каналу изменяется дискретно от 50 до 19200 бод (бит/с) при тактовой частоте микросхемы 4608 кГц. Выбор скорости обмена производится заданием комбинаций уровней на входах FR0-FR3 (их возможное сочетание приведено в табл. 7.7).

Следует отметить, что микросхема имеет выводы HALT, VIRQ и RPLY с открытым стоком, имеющим UOL низкого уровня. Для обеспечения на данных выходах высокого уровня необходимо между выходом и шиной источника питания UCC (+5 В) включить резистор с номинальным значением, рассчитанным исходя из значения выходного тока логического 0 IOL (не более 3,2 мА).

Для работы БИС К1801ВП1-035 со специальными линиями типа линий с токовыми петлями, телеграфным интерфейсом и т. п. необходимы специальные схемы сопряжения.

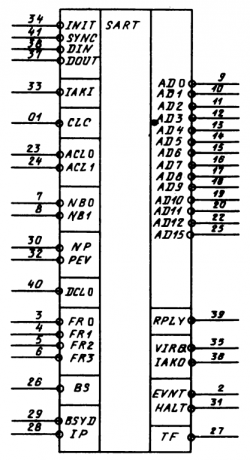

На рис. 7.8 приведены условные графические обозначения К1801ВП1-035. Более подробно описание БИСМ изложено в [25].

| Номер | Обозначение | Наименование |

|---|---|---|

| 1 | CLC | Вход тактовой частоты |

| 2 | EVNT | Выход прерываний по таймеру |

| 3-6 | FR0-FR3 | Вход выбора скорости обмена |

| 7,8 | NB0, NB1 | Вход выбора формата |

| 9 | \\AD0 | Вход-выход 0-го разряда адреса-данных системной магистрали |

| 10 | \\AD1 | Тоже 1-го разряда |

| 11 | \\AD2 | Тоже 2-го разряда |

| 12 | \\AD3 | Тоже 3-горазряда |

| 13 | \\AD4 | То же 4-го разряда |

| 14 | \\AD5 | То же 5-го разряда |

| 15 | \\AD6 | То же 6-го разряда |

| 16 | \\AD7 | То же 7-го разряда |

| 17 | \\AD8 | Вход 8-го разряда адреса-данных системной магистрали |

| 18 | \\AD9 | То же 9-го разряда |

| 19 | \\AD10 | То же 10-го разряда |

| 20 | \\AD11 | То же 11-го разряда |

| 21 | GND | Общий |

| 22 | \\AD12 | Вход-выход 12-го разряда адреса-данных системной магистрали |

| 23,24 | ACL0, АСL1 | Вход выбора адреса |

| 25 | \\AD15 | Вход 15-го разряда адреса-данных системной магистрали |

| 26 | \\BS | Вход сигнала выбора внешнего устройства системной магистрали |

| 27 | \\TF | Выход сигнала передатчика |

| 28 | \\IP | Вход сигнала приемника |

| 29 | \\BSYD | Вход сигнала занятости последовательного канала |

| 30 | NP | Вход установки паритета |

| 31 | \\HALT | Выход сигнала останова системной магистрали |

| 32 | PEV | Вход установки четности или нечетности |

| 33 | \\IAKI | Вход сигнала разрешения прерывания системной магистрали |

| 34 | \\INIT | Вход сигнала установки системной магистрали |

| 35 | \\VIRQ | Выход сигнала запроса на векторное прерывание системной магистрали |

| 36 | \\IAK0 | Выход сигнала разрешения прерывания системной магистрали |

| 37 | \\DOUT | Вход сигнала управления выводом данных системной магистрали |

| 38 | \\DIN | Вход сигнала управления ввода данных системной магистрали |

| 39 | \\RPLY | Вывод сигнала ответа приемника информации системной магистрали |

| 40 | \\DCLO | Вход сигнала «Авария источника питания» |

| 41 | \\SYNC | Вход сигнала синхронизации обмена системной магистрали |

| 42 | UCC | Напряжение источника питания |

| Название | Адрес | |||

|---|---|---|---|---|

| группы 1 | группы 2 | группы 3 | группы 4 | |

| Регистр состояния приемника | 177 560 | 176 560 | 176 570 | XXXXX0 |

| Буферный регистр приемника | 177 562 | 176 562 | 176 572 | XXXXX2 |

| Регистр состояния передатчика | 177 564 | 176 564 | 176 574 | XXXXX4 |

| Буферный регистр передатчика | 177 566 | 176 566 | 176 576 | XXXXX6 |

| Адрес вектора прерывания приемника | 060 | 360 | 370 | XX0 |

| Адрес вектора прерывания передатчика | 064 | 364 | 374 | XX4 |

| Скорость обмена, бод | FR3 | FR2 | FR1 | FR0 |

|---|---|---|---|---|

| 50 | 0 | 0 | 0 | 0 |

| 75 | 0 | 0 | 0 | 0 |

| 100 | 0 | 0 | 1 | 0 |

| 150 | 0 | 0 | 1 | 1 |

| 200 | 0 | 1 | 0 | 0 |

| 300 | 0 | 1 | 0 | 1 |

| 600 | 0 | 1 | 1 | 0 |

| 1200 | 0 | 1 | 1 | 1 |

| 2400 | 1 | 0 | 0 | 0 |

| 4800 | 1 | 0 | 0 | 1 |

| 9600 | 1 | 0 | 1 | 0 |

| 19 200 | 1 | 0 | 1 | 1 |

| 57 600 | 1 | 1 | 0 | 0 |

Литература

В. Г. Домрачев и др. Базовые матричные кристаллы и матричные БИС. — Энергоатомиздат, 1992. — ISBN 5-283-01597-1

В. Г. Домрачев и др. Базовые матричные кристаллы и матричные БИС. — Энергоатомиздат, 1992. — ISBN 5-283-01597-1 Н. Н. Аверьянов и др. / Под ред. В. А. Шахнова. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2-х т.. — Радио и связь, 1988. — Т. 2.

Н. Н. Аверьянов и др. / Под ред. В. А. Шахнова. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2-х т.. — Радио и связь, 1988. — Т. 2.