Контроллер дисковода: схемотехника и принципы работы

КАНАЛ ЗАПИСИ

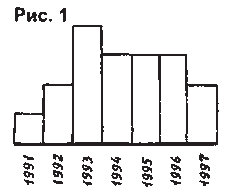

Количество статей в журналах «Радиолюбитель», «Радиолюбитель. Ваш компьютер» за 1993…1997 годы, посвященных схемотехнике контроллеров дисководов [1,2], явно снижается (рис.1).

Однако тема гибких магнитных дисков (ГМД) еще не закрыта. Дисководы или накопители на гибких магнитных дисках (НГМД) входят в состав как бытовых, так и мощных профессиональных компьютеров.

Помочь разобраться в тонкостях работы основных узлов контроллеров НГМД, отвечающих за запись-воспроизведение информации, призвана эта статья.

Изложение материала построено по принципу «логической цепочки» — из предыдущего вытекает последующее. Некоторые тезисы для лучшего понимания освещаются в упрощенном виде.

СТРУКТУРНАЯ СХЕМА КОНТРОЛЛЕРА НГМД

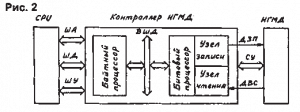

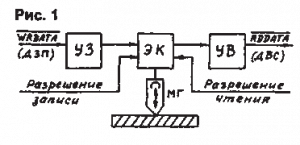

На рис.2 приведена обобщенная структурная схема контроллера НГМД, в которой особо выделены интересующие нас цепи записи и чтения информации.

Компьютер (CPU) сообщается с контроллером, как правило, через специальный системный разъем. Для сопряжения используются сигналы шины адреса (ША), шины данных (ШД) и шины управления (ШУ). Количество упомянутых сигналов и их конфигурация зависят от типа компьютера.

Функционально контроллер НГМД можно рассматривать как взаимосвязанную систему параллельного (байтного) и последовательного (битового) специализированных процессоров [3].

Байтный процессор реализует функцию сопряжения с CPU, организует командный режим управления накопителем, анализирует состояние НГМД и контроллера. Схемная реализация байтного процессора варьируется в зависимости от компьютерной платформы.

Более того, даже внутри однотипной платформы «ZX-SPECTRUM» известно по крайней мере четыре различных дисковых интерфейса: «Beta 128 Disk Interface», «Disciple», «Delta Disk Interface», «Discovery 1». Каждый интерфейс предполагает в первую очередь отличия в байтном процессоре.

Функции битового процессора заключаются в организации последовательно-параллельного преобразования, кодировании записываемой информации, синхронизации, декодировании данных, обнаружении и коррекции ошибок обмена с накопителем. Битовый процессор сообщается через внутреннюю шину данных (ВШД) с байтным процессором. Схемотехника битового процессора в достаточной мере упорядочена и унифицирована.

Узлы записи и чтения являются передаточным звеном между битовым процессором и дисковым накопителем. Весь набор интерфейсных линий связи удобно представить в виде глобальной двунаправленной магистрали сигналов управления (СУ), а также сигналов данных записи (ДЗП) и данных воспроизведения (ДВС).

Для того чтобы более четко представлять взаимодействие узлов записи и чтения с остальными элементами схемы, рассмотрим основные направления в схемотехнике контроллеров НГМД.

ОСОБЕННОСТИ ПОСТРОЕНИЯ КОНТРОЛЛЕРОВ НГМД

При разработке контроллеров дисководов специалисты руководствуются следующими принципами:

- доступность элементной базы;

- простота конструкции;

- оригинальность технического решения.

По мере накопления опыта электрические схемы совершенствуются и оптимизируются.

Одна из самых простых для повторения схем контроллера НГМД была предложена для домашнего компьютера «Специалист» [4]. Решение задачи на основе последовательного порта КР580ВВ51А привело к нестандартной форме записи и низкой информационной емкости дискеты — всего лишь 144 Кб.

Более удачной оказалась попытка использования логических элементов низкой и средней степени интеграции в контроллере для компьютера «Радио-86РК» [5]. В результате появилось технически оригинальное, грамотное, но специализированное решение. Емкость дискеты не превышала 400 Кб.

Качественный скачок произошел с началом массового выпуска и применения БИС контроллера НГМД КР1818ВГ93 (в дальнейшем по тексту — ВГ93). Большинство существующих схем любительских контроллеров дисководов базируется именно на ВГ93, позволяющей размещать на двусторонней дискете до 800 Кб полезной информации.

Схема применения БИС, предложенная разработчиками в 1986 году [6], стала основой для дальнейших модификаций. Владельцы самодельных «ZX-SPECTRUM» в 1989 г. имели возможность собрать одноплатный вариант компьютера «ПЕНТАГОН-48» со встроенным контроллером НГМД на базе ВГ93.

ТРИ ПОКОЛЕНИЯ БИС-КОНТРОЛЛЕРОВ

Как известно, ВГ93 была создана по образу и подобию БИС WD1793 фирмы Western Digital [3]. Обе эти микросхемы можно условно отнести к первому поколению БИС (табл.1).

Табл.1

| ПОКОЛЕНИЕ | БИС | ФУНКЦИЯ |

|---|---|---|

| Первое | КР1818ВГ93, КР1810ВГ72, КМ1821ВГ72, WD179X, WD279x, i8272(A), μPD765(A), CM609 | Программируемый контроллер НГМД |

| Второе | i82072, HPD76062, NSDP8473 | Высокоинтегрированный контроллер НГМД |

| Третье | СБИС-чипы | Встроенный контроллер НГМД |

«Прародителем» БИС контроллеров дисководов следует признать микросхему μPD765 японской фирмы NEC (Nippon Electric Co.), разработанную в конце 70-х годов. Ее применение уменьшило число применяемых микросхем в контроллере НГМД в 20 раз!

«Вторым» поставщиком БИС стала американская (Intel Corp., объявившая в 1980 году о начале выпуска функционально совместимого аналога μPD765 — микросхемы i8272. Модифицированный вариант этой БИС (i8272A, отечественный аналог — КР1810ВГ72) стал базовой моделью схем первого поколения и установил стандарт «де-факто» на управление НГМД в компьютерах IBM PC XT/AT. В радиолюбительской практике данный тип контроллера был успешно применен в блочно-модульной микроЭВМ, разработанной на базе схемы «Микро-80» [2].

В обрамление БИС первого поколения обычно входит дополнительно до двух десятков корпусов логических схем.

Микросхема ВГ93 совместима с i8272A по программно-аппаратному интерфейсу, но имеет более упрощенную структуру и пониженную тактовую частоту. Кроме того, для ее питания требуется два, а не один источник напряжения.

В контроллерах второго поколения используются СБИС типа Intel i82072, NEC μPD76062, NSDP8473 в комплекте с 3…8 дополнительными микросхемами. Эти контроллеры имеют расширенный набор команд, обеспечивающий совместимость с i8272A, a также встроенный буфер FIFO (First Input — First Output), поддержку страничной организации дорожек и т. д. Упомянутые новшества помогают реализовать сопряжение с высокоскоростными шинами типа EISA, MCA (Micro Channel).

На современных системных платах компьютеров, подобных «PENTIUM», контроллеры НГМД входят составной частью внутрь СБИС-чипов. Это уже техника третьего поколения. Если в схемы контроллеров НГМД первых двух поколений радиолюбитель с паяльником в руках еще может попытаться внести какие-то усовершенствования, то в СБИС-чипах это сделать принципиально невозможно.

Итак, вернемся к контроллерам первого поколения. Узлы записи и чтения являются внешними по отношению к БИС. С точки зрения работы канала записи представляется важным тот факт, что БИС первого поколения позволяют осуществлять два метода кодирования — ЧМ и МЧМ. Какой же из методов лучше?

СПОСОБЫ ЗАПИСИ ИНФОРМАЦИИ НА МАГНИТНЫЙ НОСИТЕЛЬ

При магнитной записи в качестве физического носителя информации используется остаточная намагниченность ферроматериала. С помощью магнитной головки ферроматериал может намагничиваться до насыщения в одном из двух направлений: ток записи одного направления условно принимается за «+J», ток противоположного направления — за «-J», размагниченное состояние принимается за «0».

Способы записи информации подразделяются на двухуровневые («+J», «-J») и трехуровневые («+J», «0», «-J»). Существуют также двухчастотные, трехчастотные и многочастотные способы записи. И наконец, различают способы записи с целочисленной кратностью временных интервалов (например 1:2:3) и со смешанной кратностью (например 1:1,5:2).

Для разных типов физических носителей (магнитная лента, гибкий диск, жесткий диск) существуют свои оптимальные методы кодирования. В накопителях с гибкими магнитными дисками применяют два основных метода, частотную модуляцию (ЧМ) и модифицированную частотную модуляцию (МЧМ). Они, по сравнению с другими, более просты в аппаратной реализации, а также обладают важным свойством самосинхронизации.

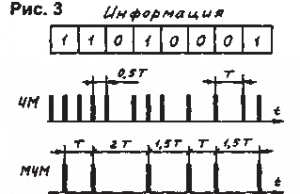

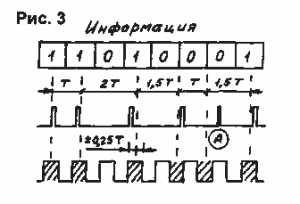

На рис 3 приведены временные диаграммы формирования сигналов ЧМ и МЧМ из исходной цифровой последовательности.

В зарубежной литературе метод ЧМ называют «манчестерским» или FM (Frequency Modulation).

Судя по рис.3, способ ЧМ можно классифицировать как двухуровневый, двухчастотный (0,5Т; Т), с целочисленной кратностью интервалов 1 2.

Способ записи МЧМ (другие названия — «код Миллера», MFM) появился позже, чем ЧМ — в конце 70-х годов. Способ МЧМ классифицируется как двухуровневый, трехчастотный (Т; 1,5Т; 2Т), со смешанной кратностью интервалов 1:1,5:2

При МЧМ на дискете можно разместить при прочих равных условиях вдвое больше цифровой информации, чем при ЧМ.

Сказанное требует пояснения. На рис.3 количество импульсов сигнала МЧМ ровно в 2 раза меньше, чем ЧМ. Если количество импульсов мысленно уравнять, то окажется, что МЧМ-сигнал позволяет переносить удвоенное количество битов данных. Метод ЧМ относят к способам записи с одинарной плотностью (SD — Single Density), а МЧМ — с двойной плотностью (DD — Double Density)

Для того чтобы реализовать высокие потенциальные возможности кода МЧМ, требуется выйти на определенный уровень технологии магнитной записи. Поэтому исторически сложилось так, что в БИС первого поколения были предусмотрены оба режима работы — как МЧМ, так и ЧМ.

В отечественной БИС ВГ93 метод ЧМ остался для совместимости с ранними моделями персональных компьютеров. Не надо забывать, что первые IBM PC работали под MS DOS 1.0 и позволяли размещать 160 Кбайт данных на односторонней дискете при ЧМ-способе записи.

В дальнейшем все выкладки будут проводиться только для МЧМ-сигналов, что характерно для подавляющего большинства домашних компьютеров

ПРОЦЕСС ЗАПИСИ ИНФОРМАЦИИ

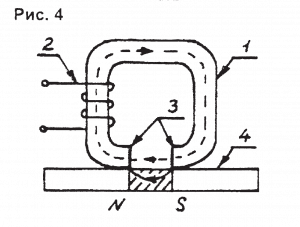

Основными элементами канала записи-чтения являются магнитная головка (МГ) и магнитная поверхность гибкого диска. По своей сути МГ является миниатюрным электромагнитом (рис. 4).

Основные части МГ — магнитопровод (1) и обмотка (2). При возникновении в обмотке перепада тока в магнитопроводе создается магнитный поток определенного направления.

В области рабочего зазора МГ (3) поток рассеивается, и часть его замыкается через магнитную поверхность дискеты (4). Таким образом создаются магнитные «отпечатки» — цепочка элементарных магнитов с полюсами N и S. которые сохраняют свою намагниченность длительное время.

Дискета представляет собой майларовый (разновидность нейлона) диск толщиной 125 мкм с тончайшим слоем ферролакового покрытия (3…5 мкм).

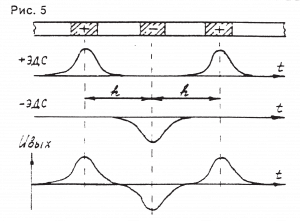

При воспроизведении процесс повторяется с точностью до наоборот. Теперь намагниченные участки, проходя мимо рабочего зазора МГ, создают магнитный поток того или другого направления, а значит — электродвижущую силу (ЭДС) в обмотке. На рис. 5 показаны несколько магнитных «отпечатков», следующих друг за другом на расстоянии h, и наводимые ими ЭДС в МГ.

Общий выходной сигнал получается при алгебраическом сложении (суперпозиции) +ЭДС и -ЭДС. Такой подход оправдан, так как в первом приближении данную систему можно считать линейной [7].

Сигналы откликов имеют колоколообразную, немного асимметричную форму и хорошо аппроксимируются функцией Гаусса. Для намагниченности «+J» сигнал имеет положительный знак, для намагниченности «-J» — отрицательный.

Суммарный выходной сигнал Uвых похож на синусоиду со «ступенькой», как в плохо настроенном усилителе мощности звуковой частоты (УМЗЧ). Однако если в УМЗЧ это катастрофический недостаток, то в магнитной записи — достоинство, поскольку из такого сигнала легче выделить цифровые «единицы» и «нули».

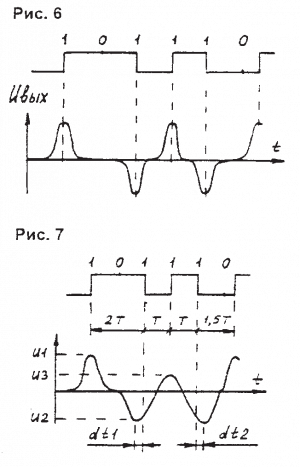

Рассмотрим, как влияет величина расстояния h на форму сигнала. Для примера выберем один и тот же МЧМ-сигнал при относительно большом (рис.6) и относительно малом (рис.7) расстоянии.

На рис. 6 максимумы выходных сигналов, как положительных, так и отрицательных, совпадают практически точно с центрами участков намагниченности. На рис.7 наблюдаются заметные смещения максимумов, известные под названием «фазовые искажения» или «сдвиг пиков». При переходе от длинного интервала (в данном примере 2Т) к короткому (Т) имеет место опережение dt1, а при переходе от короткого интервала (Т) к длинному (1,5Т) — отставание dt2. Кроме того, наблюдаются амплитудные искажения сигнала (UI > U2 > U3).

Сигнал, изображенный на рис.7. гораздо труднее правильно декодировать, чем сигнал, приведенный на рис. 6. Ситуация будет еще хуже при дальнейшем уменьшении h. «Сдвиг пиков» происходит всякий раз при переходе от любого длинного (1,5T; 2Т) к любому короткому (Т;1,5Т) интервалу и наоборот.

Применительно к гибким магнитным дискам — большие расстояния h будут наблюдаться на внешних концентрических дорожках (0, 1, 2…), а малые h — на внутренних. Для справки, реальные значения h в случае ГМД диаметром 5,25 дюйма составляют 5…10 микрон.

Теперь понятно, что проблемы, возникающие с некачественным воспроизведением информации на внутренних дорожках дискеты, носят объективный характер и будут проявляться в той или иной степени на любых типах дисководов и с любым типом дискет.

Напомним, что в отечественных домашних компьютерах стандартными, к сожалению, стали двусторонние дисководы двойной плотности диаметром 5,25 дюйма типа МС5305, МС5311, МС5313, МС5350, ЕС5321.01 (Болгария), Robotron K5601/CM5643 (Германия), FD55A-F (Япония).

«К сожалению» — потому что в конце 80-х годов мировой парк дисководов был практически полностью обновлен за счет более качественных и емких моделей дисководов 5,25 дюйма (1.2 Мб) и 3,5 дюйма (0,72; 1,44; 2,88 Мб). Новые технологии изготовления магнитных головок, жесткие допуски на электромеханический привод, улучшенная конструкция дискет — все это сводит к минимуму фазовые искажения.

Если бы с самого начала в любительских конструкциях применялись дисководы 3,5 дюйма, то при той же схемотехнике контроллеров НГМД проблем с некачественным чтением программ было бы значительно меньше.

Какие же меры предпринимаются в контроллерах дисководов для сведения к минимуму фазовых искажений?

СТРУКТУРНАЯ СХЕМА УЗЛА ЗАПИСИ

В БИС контроллеров НГМД первого поколения обычно предусматриваются две основные защитные меры:

1) выдача сигналов предкомпенсации записи SR, SL для ВГ93 или PS0, PS1 для i8272(А);

2) выдача сигнала TR43 для ВГ93 или LCT для i8272(A), информирующего о нахождении магнитной головки за сорок третьей дорожкой, то есть в «опасной» зоне. Эти сигналы могут применяться самостоятельно в случае НГМД, имеющих специальный вход LCT (Low CurrenT), для уменьшения тока записи на внутренних дорожках дискеты. В интерфейсе дисководов 5,25 дюйма для домашних компьютеров вход LCT не используется. В этом можно удостовериться, посмотрев на незадействованный контакт 2 разъема сопряжения контроллера с дисководом.

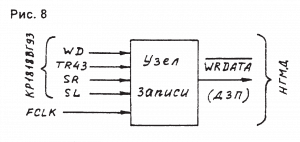

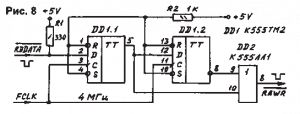

На рис.8 представлена обобщенная структурная схема узла записи контроллера НГМД, выполненного на базе ВГ93.

| ФУНКЦИЯ | SR | SL | ПРИМЕЧАНИЕ |

|---|---|---|---|

| Нормальная работа | 0 | 0 | Сдвиг сигнала -WRDATA отсутствует |

| Отставание | 1 | 0 | Сдвиг вправо сигнала -WRDATA для компенсации расстояния dt: (рис.7) |

| Опережение | 0 | 1 | Сдвиг влево сигнала -WRDATA для компенсации расстояния dt: (рис.7) |

| Переходный процесс | 1 | 1 | Недокументированная комбинация |

Не все сигналы из указанных на структурной схеме могут быть задействованы в конкретном контроллере. Приведем их расшифровку и параметры для метода МЧМ при тактовом сигнале CLK частотой 1 МГц на выводе 24 ВГ93 [8]:

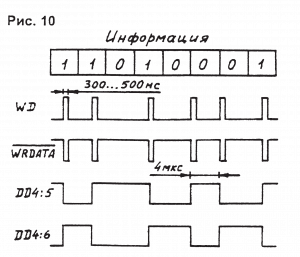

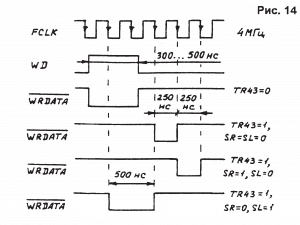

WD (Write Data) — «запись данных», импульсы положительной полярности длительностью 300…500 нс с периодом 4; 6; 8 мкс (соответственно Т; 1,5Т; 2Т на рис.3);

TR43 (TRack 43) — «нахождение магнитной головки за дорожкой 43», низкий логический уровень означает дорожки 0…43, высокий логический уровень — дорожки 44 и выше, причем верхний предел ог-раничивается не числом 76 [6], а количеством дорожек в режиме максимального форматирования, то есть 82…84;

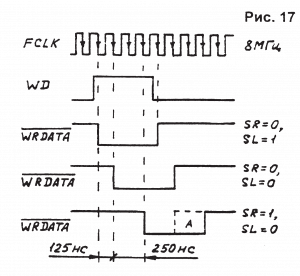

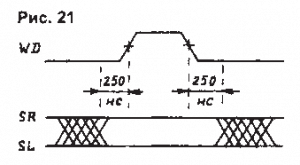

SR, SL (Shift Right, Shift Left) — «сдвиг вправо», «сдвиг влево», сигналы управления предкомпенсацией при записи, используются согласно алгоритму табл.2;

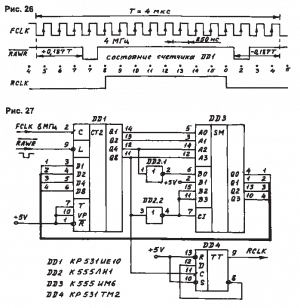

FCLK (Frequency CLocK) — «тактовые импульсы», чаще всего имеют форму меандра с частотой 4 МГц или 8 МГц;

WRDATA (WRite DATA) — «данные записи на дисковод (ДЗП)», выходной сигнал контроллера, импульсы отрицательной полярности с длительностью 0,15…2,5 мкс и периодом 4; 6; 8 мкс [9].

Рассмотрим конкретные схемотехнические решения узлов записи. Нумерация выводов микросхем, их позиционные обозначения, серии, типономиналы в разных моделях контроллеров будут разными. Однако это не меняет сути вопроса, читатели без труда узнают знакомые очертания своих схем.

ЭЛЕКТРИЧЕСКИЕ СХЕМЫ УЗЛОВ ЗАПИСИ

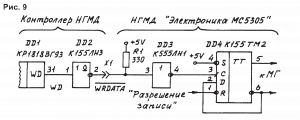

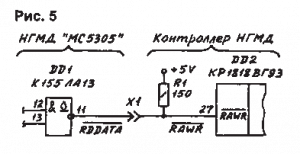

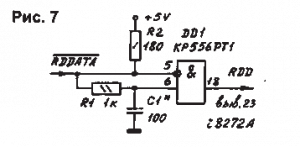

Если сравнить между собой временные параметры сигналов WD и -WRDATA, можно понять, почему, вопреки рекомендациям разработчиков [6], работает схема простейшего узла записи, приведенная на рис.9 (CPU «Балтик», «Эрик»).

Выходной сигнал контроллера WRDATA получается путем логического инвертирования сигнала WD. Это возможно, так как допуски на длительность WRDATA больше, чем на WD. Далее -WRDATA через разъем X1 по кабелю поступает в дисковод. Для примера выбран отечественный НГМД МС5305.

Нагрузкой инвертора с открытым коллектором DD2 является низкоомный резистор R1. Инвертор DD3 увеличивает крутизну фронта сигнала, подаваемого на синхровход триггера DD4.

При высоком уровне сигнала «Разрешение записи» триггер обеспечивает деление на 2 входной час тоты (рис. 10).

Это понятно, так как цифровую информацию несет не длительность WRDATA, а его период.

С парафазных выходов триггера сигнал записи поступает через диодно-резистивный коммутатор на магнитную головку (МГ).

Небольшая тонкость. Запись происходит благодаря перепадам тока в МГ. Ширина элементарного магнитного «отпечатка» определяется в первую очередь конструкцией МГ и параметрами ферроматериала дискеты.

Как видно, длительность сигнала -WRDATA принципиального значения не имеет, важно, чтобы расстояние между передними фронтами импульсов было жестко сфазировано и не «плавало».

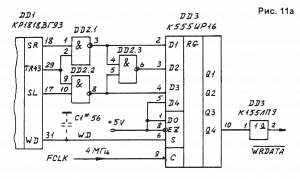

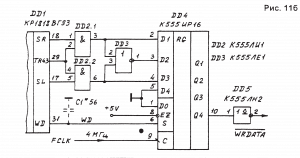

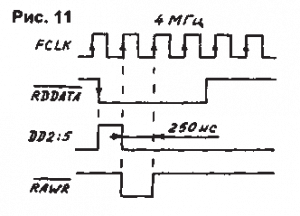

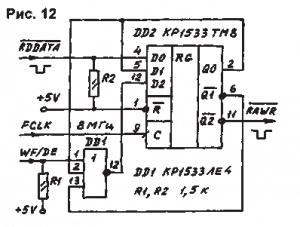

Информация, записанная при помощи приведенной схемы, как правило, без вопросов считывается с внешних дорожек дискеты, а при ювелирной юстировке дисковода, фирменной сборке, высоком качестве дискет — и с внутренних дорожек. Возможность обмена записями с коллегами все-таки остается проблематичной, так как при смене дисковода уверенное чтение информации с последних дорожек не гарантируется из-за эффекта «сдвига пиков». Разработчики быстро оценили недостатки простейшей схемы и перешли к более сложным (рис. 11а — CPU «ОРИОН-128», рис.11б — CPU «ATM-TURBO-2»).

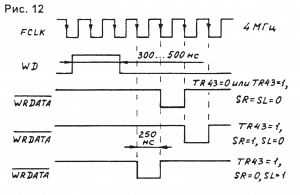

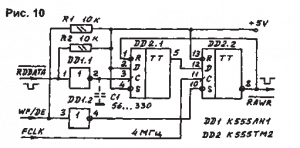

Во-первых, в этих схемах длительность импульса выходного сигнала -WRDATA стала меньше по сравнению с исходным WD практически в 2 раза — 250 нс вместо 300…500 нс. Суть нововведения не столько в самой величине длительности, сколько в принудительной фазировке и переднего, и заднего фронтов сигнала.

Во-вторых, для уменьшения фазовых искажений вводится предкомпенсация сигналов -WRDATA при записи начиная с сорок четвертой дорожки и далее.

При неустойчивой работе регистра в подобных схемах иногда вводят конденсатор С1* (показан пунктиром), который сдвигает во времени импульсные последовательности на входах S и С. Другое решение — инверсия сигнала FCLK.

Поясняющие временные диаграммы приведены на рис.12.

Логика функционирования обеих схем идентична. Разница заключается в инверсии некоторых внутрисхемных сигналов, что не имеет большого значения.

Принцип работы узла защиты заключается в том, что по переднему фронту сигнала WD в сдвиговый регистр К555ИР16 заносится код, определяемый логическими уровнями на входах Dl…D4. По окончании сигнала WD этот код выводится из регистра в последовательном виде через выход Q4 синхроимпульсами FCLK (4 МГц). Период повторения синхроимпульсов FCLK составляет 250 нс, что и определяет длительность выходного сигнала -WRDATA.

В зависимости от комбинации сигналов SR, SL, TR43, на выходе формируют импульсы одинаковой длительности, сдвинутые друг относительно друга на 250 нс. Компенсация фазовых искажений происходит автоматически — ВГ93 сам «знает», когда выдавать сигналы SR и SL.

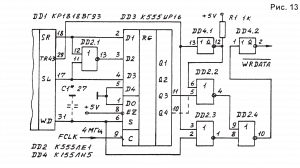

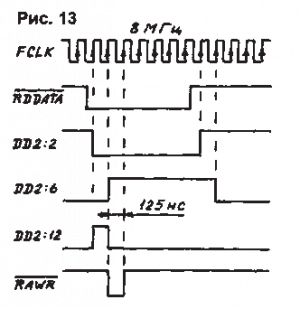

На рис.13 показан случай, когда в некоторых контроллерах сигнал снимается не с выхода Q4, а с выхода Q3 регистра. К чему это приводит?

Для записи без предкомпенсации (SR=0, SL=0) и для записи с отставанием (сдвиг вправо) (SR=1, SL=0) форма импульсов остается прежней. Однако для записи с опережением (сдвиг влево) (SR=0, SL=l) длительность импульса -WRDATA расширяется и становится равной 500 нс (рис. 14).

Нельзя признать это логичным и оправданным, поскольку тем самым вводится непропорционально большое значение сдвига влево. Схему рис.13 легко привести к стандартному виду перепайкой цепи от вывода 11 к выводу 10 микросхемы DD3 (показано пунктиром).

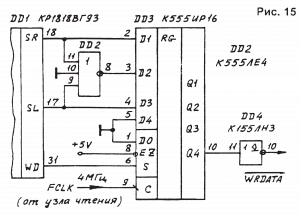

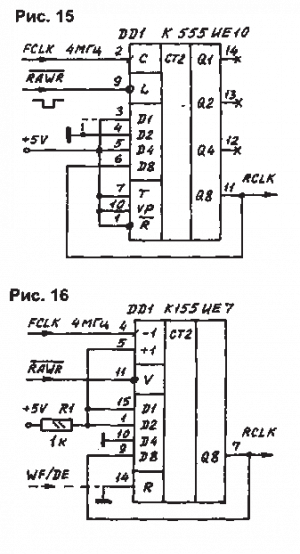

Еще одна разновидность схем с применением регистра К555ИР16 изображена на рис.15 (CPU «KAY-256»).

Отличительная особенность схемы — отсутствие сигнала TR43, то есть предкомпенсация производится для всех без исключения дорожек — как внешних, так и внутренних.

Логика простая — на внешних дорожках условия для считывания хорошие, и некоторая «перекомпенсация» не ухудшает параметры чтения, так как расстояние между участками с разной намагниченностью (рис.6) достаточно велико. Напротив, при приближении к дорожке с номером 43 в данном случае происходит плавное наращивание задержек отставания/опережения. Следовательно, исчезают проблемы с неустойчивым чтением информации в районе 40…43-й дорожек для некоторых типов дисководов.

К нюансам схемы относится применение не совсем чистого меандра FCLK 4 МГц, который поступает со схемы цифрового выделения данных узла чтения. Такое решение упрощает общую схему контроллера, но не ухудшает параметры, так как в режиме записи этот сигнал все равно остается строгим меандром.

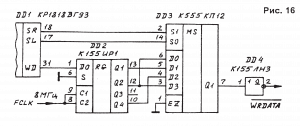

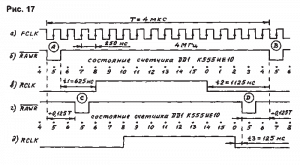

Дальнейшее развитие темы предложено в схеме рис. 16, временные диаграммы работы которой представлены на рис. 17 (усовершенствованный контроллер для CPU «ВЕКТОР-06Ц»).

Сдвиговый регистр выполнен на микросхеме К155ИР1. Важной особенностью схемы является увеличение тактовой частоты FCLK с 4 МГц до 8 МГц. За счет этого появляется возможность установить задержку предкомпенсации равной 125 нс, что вдвое меньше по сравнению с предыдущими схемами.

Имеется еще одна особенность схемы, очень привлекательная с точки зрения практики. Связка «регистр К155ИР1 — мультиплексор К555КП12» позволяет установкой перемычек изменять время предкомпенсации в довольно широких пределах отдельно для сдвига вправо и отдельно для сдвига влево. Таким образом, можно оптимально учесть особенности конкретного типа дисковода.

Как известно, величина «сдвига пиков» при записи зависит от массы факторов и однозначному расчету не поддается. Ее определяют опытным путем. Например, по мнению авторов схемы, изображенной на рис.16, для японских 80-дорожечных дисководов ТЕАС (FD-55) лучше подходят задержки: опережения 125 нс и отставания 250 нс

Данный факт не противоречит теории [7], согласно которой реальные отклики магнитных «отпечатков» имеют асимметричную форму вследствие эффекта саморазмагничивания и нелинейности перехода намагниченности носителя.

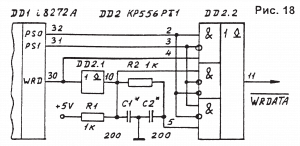

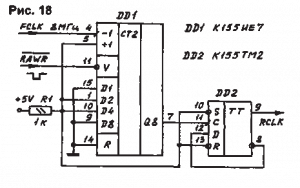

Подбор задержки предкомпенсации предлагают и разработчики универсальной платы контроллера #МС5301 (рис.18), выполненной на базе i8272А [10]. Конденсаторами С1* и С2* устанавливают задержки соответственно опережения и отставания. Все логические связи выполнены внутри программируемой матрицы DD2, что позволяет максимально упростить конструкцию. Особенность схемы — отсутствие жесткой фазировки выходных сигналов из-за RC формирователей.

При этом период сигнала WRDATA в большей степени подвержен изменению вследствие температурных колебаний, нестабильности питающего напряжения и наводок.

ОПТИМАЛЬНЫЕ РЕШЕНИЯ

Проведем сравнение рассмотренных любительских конструкций со схемами, применяемыми в промышленной аппаратуре. В частности, в персональной ЭВМ «ЭЛЕКТРОНИКА МС0585» контроллер НГМД выполнен на базе ВГ93, работающей в паре со специализированным 8-разрядным микропроцессором.

В этом контроллере применяется только метод записи МЧМ (на ЧМ ресурсы даже и не тратятся!). Логика работы узла записи «спрятана» в матрице КР556РТ4А. Контроллер обеспечивает трехступенчатую предкомпенсацию выходных сигналов -WRDATA:

- 125 нс для дорожек 0…43;

- 250 нс для дорожек 44…60;

- 375 нс для дорожек 61 …79.

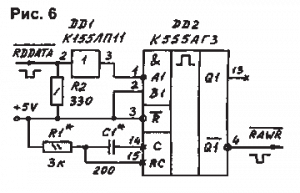

Длительность сигнала -WRDATA определяется выходным одновибратором К555АГЗ и имеет величину порядка 240…280 нс, причем передний фронт сигнала жестко сфазирован.

Трехступенчатая предкомпенсация в любительских контроллерах, по всей видимости, недостижима, поскольку не просматривается простой способ организовать выдачу сигнала TR60, свидетельствующего о нахождении магнитной головки за дорожкой с номером 60.

Абсолютным значениям предкомпенсации, принятым в ЦПУ «ЭЛЕКТРОНИКА МС0585», можно доверять хотя бы потому, что схема прошла значительную модернизацию по сравнению с ее первоначальным вариантом [6]. Поэтому для любительских конструкций оптимальным видится двухступенчатый расклад: 125 нс предкомпенсации для дорожек 0…43, 250 нс — для остальных дорожек, длительность сигнала -WRDATA — 250…500 нс.

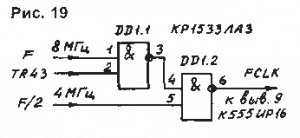

Схемы, изображенные на рис.11а, 11б, 13,15, можно приблизить к оптимальным.

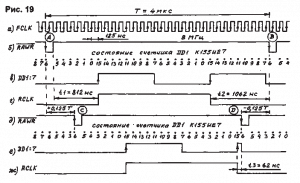

Для этого тактовые синхроимпульсы на входы регистров К555ИР16 следует подавать переменной частоты (рис.19): 8 МГц — для дорожек 0…43 (предкомпенсация — 125 нс, длительность сигнала -WRDATA — 125 нс); 4 МГц — для остальных дорожек (предкомпенсация — 250 нс, длительность сигнала -WRDATA — 250 нс).

При этом в схемах рис. 11а, 11б сигнал TR43 следует отсоединить от элементов DD2.1, DD2.2, а на его место постоянно подавать логический «0».

Некоторое неудобство создает уменьшение на внешних дорожках длительности сигнала -WRDATA до 125 нс. Как правило, дисководы допускают работу с такими сигналами, что подтверждается практикой. Номинал нагрузочного резистора R1 (рис.9) при этом необходимо уменьшить до 150 Ом.

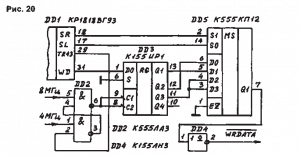

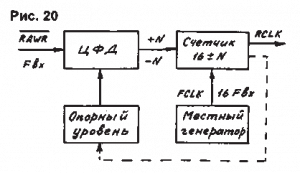

Схему, изображенную на рис. 16, можно доработать аналогичным образом (рис.20).

Длительность выходного сигнала -WRDATA, как и прежде, составляет 500 нс. Предкомпенсация влево-вправо для дорожек 0…43 — 125 нс, для остальных дорожек — 250 нс.

Внимательный читатель, наверное, обратил внимание на то, что в схеме рис. 20 имеется еще одно новшество — вход D3 мультиплексора К555КП12 подключен не к выводу Q2 регистра К155ИР1, а к выводу Q3. Казалось бы, какая разница?

Для ответа на этот вопрос сначала нужно разобраться, зачем вообще используется вход D3 мультиплексора? Получается, что схема ориентируется на случай, когда SR=SL=1. Такая комбинация сигналов представляется нелогичной — нельзя же одновременно вводить и отставание, и опережение (табл.2).

Однако существуют моменты времени, когда состояние SR=SL=1 возможно. Чтобы в этом убедиться, достаточно подключить входы логического элемента 2И-НЕ (К555ЛАЗ) к выводам 17, 18 ВГ93 и посмотреть логическим пробником сигнал на его выходе. Пробник будет постоянно «подмаргивать» в режиме записи информации на дисковод.

Согласно техническим данным на ВГ93 [8], сигналы SR и SL должны иметь привязку к WD, как показано на рис. 21.

Нетрудно заметить, что в моменты смены состояний SR и SL на переходном этапе могут одновременно наблюдаться их единичные уровни.

Более тонкие эксперименты показывают, что промежуток времени, когда SR=SL=1, имеет продолжительность около 500 нс и совпадает по времени с зоной, обозначенной на рис.17 буквой «А». Это означает, что иногда сигнал -WRDATA на осциллограмме для случая SR=1, SL=0 будет иметь укороченную до 250 нс длительность.

Чтобы этого не происходило, следовало бы в схеме рис. 16 отсоединить вывод 3 микросхемы DD3 от вывода 12 микросхемы DD2 и присоединить его к выводу 10 микросхемы DO2. С такой доработкой функционирование схемы станет чуть более корректным. При одной и той же длительности сигнала -WRDATA, его прохождение по кабельному тракту сопровождается одними и теми же амплитудно-фазовыми искажениями.

Аналогичный принцип положен в основу схемного решения, приведенного на рис.20.

Для разновидностей узлов записи, выполненных без мультиплексора, данный нюанс учитывать не надо, поскольку ввод информации в регистр К555ИР16 производится во время действия сигнала WD. При этом комбинация сигналов SR=SL=1 физически невозможна.

ОБОБЩЕНИЕ РЕЗУЛЬТАТОВ

1. Длительность сигнала WRDATA не имеет решающего значения и может варьироваться в пределах 250…500 нс. Желательно, чтобы ее величина не менялась при разных сочетаниях сигналов SR, SL, TR43.

2.Передний фронт сигнал WRDATA должен быть жестко синхронизирован тактовыми импульсами внутреннего кварцевого генератора контроллера НГМД.

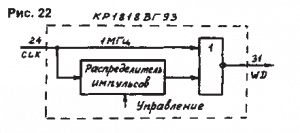

3. В качестве сигнала -WRDATA, допускается использовать проинвертированный сигнал WD микросхемы ВГ93, так как он имеет "привязку к тактовым импульсам CLK. Внутреннее формирование сигнала WD происходит примерно по следующей схеме (рис. 22).

Длительность единичного уровня сигнала WD соответствует длительности нулевого уровня сигнала CLK что подтверждают эксперименты с подачей на вход CLK импульсов разной скважности.

Широкий допуск на длительность сигнала WD (300…500 нс) приводится в справочных данных с некоторым запасом. Для тактовой частоты CLK 1 МГц длительность WD составляет величину, близкую к 500 нс.

4. В идеальном случае величина предкомпенсации должна дискретно увеличиваться маленькими «шажками» от нулевой дорожки и далее. На практике ограничиваются кусочно-линейной аппроксимацией с одной двумя или тремя ступенями.

Оптимальной для дисководов 5,25 дюйма емкостью 800 Кб можно считать двухступенчатую предкомпенсацию: 125 нс — для дорожек 0…43 и 250 нс — для остальных дорожек.

5. Одноступенчатые схемы предкомпенсации (рис.15, 16, 18) более просты в исполнении. Они позволяют устранить нечеткое чтение информации в области дорожек 40…43.

6. Следует учитывать, что некоторые типы дисководов имеют встроенный режим автоматического уменьшения тока записи на дорожках со старшими номерами. Имеется в виду внутренняя предкомпенсация без использования входа LCT.

Теоретически, чем меньше ток записи, тем меньше намагниченность «отпечатка», а значит, меньше амплитуда выходного сигнала и меньше «сдвиг пиков». Следует отметить, что в дисководе ЕС5321.01 ток записи автоматически уменьшается начиная с 64-й дорожки, в дисководе FD-55 (ТЕАС) — с 44-й дорожки, в дисководах МС5305…МС5313 данная функция вообще не предусмотрена. Таким образом, фазовая коррекция в контроллере НГМД может накладываться на внутреннюю фазовую коррекцию в дисководе. Результат непредсказуем. Теперь становится понятной важность подбора оптимальной величины предкомпенсации для каждого конкретного дисковода.

7. Обобщенные параметры рассмотренных схем узлов записи приведены в табл.3.

Табл. 3

| СХЕМА | ДОРОЖКИ 0…43 | ДОРОЖКИ 44 И БОЛЕЕ | ||||

|---|---|---|---|---|---|---|

| СДВИГ ВПРАВО | СДВИГ ВЛЕВО | ДЛИТЕЛЬНОСТЬ -WRDATA | СДВИГ ВПРАВО | СДВИГ ВЛЕВО | ДЛИТЕЛЬНОСТЬ -WRDATA | |

| Рис.9 | 0 | 0 | WD | 0 | 0 | WD |

| Рис.11а, б | 0 | 0 | 250 нс | 250 нс | 250 нс | 250 нс |

| Рис.13 | 0 | 0 | WD | 250 нс | 500 нс | 250 нс, 500 нс |

| Рис 15 | 250 нс | 250 нс | 250 нс | 250 нс | 250 нс | 250 нс |

| Рис 16 | 250 нс | 125 нс | 500 нс, 250 нс | 250 нс | 125 нс | 500 нс, 250 нс |

| Рис.18 | 200…300 нс | 200…300 нс | WD | 200…300 нс | 200…300 нс | WD |

| Оптимальная | 125 нс | 125 нс | 250…500 нс | 250 нс | 250 нс | 250…500 нс |

8. Все любительские схемы, как правило, прошли хорошую практическую «обкатку» не на одной тысяче дисководов. Поэтому трудно ставить под сомнение те или иные технические решения, если они удовлетворяют пользователей.

Узнав физическую подоплеку процессов, происходящих в узле записи, читатель вправе сам выбрать подходящую схему. Однако не следует ожидать сразу феноменальных результатов. Нельзя исключить того, что при хорошем дисководе, качественных дискетах и удачно примененной схеме узла чтения заметного улучшения работы не будет заметно.

Здесь не случайно сделан акцент на качественное исполнение узла чтения, поскольку многие отмечают его решающую роль в работе контроллера, НГМД.

Этот вопрос требует отдельного освещения.

Литература

- Радиолюбитель. — 1991, N5; 1992, N11; 1993, NN 2, 4, 6, 12; 1994, NN2, 4, 11; 1995, NN3,4,7.

- Радиолюбитель. Ваш компьютер:—1996, NN5,8, 10; 1997, NN2,7.

- Справочник по персональным ЭВМ/Н. И. Алишев и др. — К.: Тэхника, 1990.

- Женжеруха А. Вместо кассеты — дискета. — Моделист-конструктор, 1989, N10, С.26.

- Седов Е., Матвеев А. Контроллер накопителя на гибких магнитных дисках для «Радио-86РК». — Радио, 1993, N1, C.13;N2, C.17.

- Коваленко В. и др. БИС контроллера КР1818ВГ93 для накопителя на гибком диске. — Микропроцессорные средства и системы, 1986, N3, С. З.

- Рыжков В. А. и др. Внешние запоминающие устройства на магнитном носителе. — М.: Энергия, 1978.

- Микросхема КР1818ВГ93. Технические условия бК0.348.877-08ТУ.

- Накопитель на гибких магнитныхдисках «Электроника МС5305». Формуляр ЛУКФ.467616.001ФО.

- Щелкунов Н., Дианов А. Организация контроллеров ГМД. — Микропроцессорные средства и системы, 1990, N4, С.70.

КАНАЛ ЧТЕНИЯ

Самая качественная схема канала записи ничего не стоит, если плохо работает канал чтения. С таким утверждением трудно не согласиться, когда речь идет о контроллерах дисководов для домашних компьютеров типа «ОРИОН-128», «ВЕКТОР-06Ц», «ZX-SPECTRUM».

Многие отмечают, что в 70…80 % случаев улучшение работы контроллера зависит от примененного алгоритма считывания информации. Этим объясняется многоликость схемных решений канала чтения, в каждом из которых есть свое рациональное зерно.

При рассмотрении принципа работы канала чтения предполагается, что читатель знаком с основными положениями техники цифровой магнитной записи [1].

ПРОЦЕСС СЧИТЫВАНИЯ ИНФОРМАЦИИ

Запись, хранение и считывание цифровой информации в накопителях с гибкими магнитными дисками (НГМД) выполняет совмещенный аналоговый канал записи-чтения (рис.1).

Как известно, применяемые в радиолюбительской практике 80-дорожечные 5,25-дюймовые дисководы используют универсальную магнитную головку (МГ). Она соединяется с трактом через электронный коммутатор (ЭК) и может работать на запись по сигналу «Разрешение записи» или на чтение по сигналу «Разрешение чтения».

Усилитель воспроизведения (УВ) имеет специально подобранную частотную характеристику. Общий коэффициент усиления УВ может меняться в процессе работы. Например у болгарских дисководов ЕС5321.01 усиление автоматически увеличивается, если МГ находится в зоне за 63-й дорожкой. Тем самым компенсируются потери от снижения тока записи на внутренних дорожках дискеты.

Сигнал -RDDATA (другое название — ДВС, «данные воспроизведения») является выходным для дисковода. По кабелю связи он поступает на одноименный вход контроллера через вывод 30 интерфейсного разъема.

Усилитель записи (УЗ) работает с входным сигналом -WRDATA (другое название — ДЗП, «данные записи»). Этот сигнал поступает от контроллера через вывод 22 разъема. Принцип его формирования и схемные особенности подробно рассмотрены в [1].

Канал чтения воспроизводит информацию в том виде, в каком она была записана. Известно, что в любительских контроллерах НГМД основным способом записи является «модифицированная частотная модуляция» (МЧМ).

САМОСИНХРОНИЗАЦИЯ КОДА МЧМ

Ранее отмечалось [1], что МЧМкод относится к классу самосинхронизирующихся. При анализе узла записи это обстоятельство не имело никакого значения. Иное дело — узел чтения.

Вспомним три правила построения сигнала МЧМ:

- «нулю» информации всегда соответствует перепад тока записи в начале цифровой позиции, занимаемой этим «нулем»;

- «единице» информации соответствует перепад тока в центре позиции, занимаемой этой «единицей»;

- «нуль» не вызывает переключение тока в том случае, если предыдущий знак — «единица».

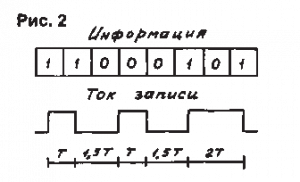

На рис.2 изображен пример построения сигнала МЧМ по приведенным выше правилам.

Таким образом, если на запись поступают или одни «единицы», или одни «нули», то перепады тока следуют через время Т. Переходу от «единиц» к «нулям» и наоборот соответствует интервал 1,5Т. И, наконец, при кодовой последовательности «101» возникает интервал 2Т.

Сигналы информации в цифровой магнитной записи должны иметь привязку к меткам времени, иначе «единицу» невозможно будет отличить от «нуля». Физическим воплощением меток времени служит синхросигнал или, по-другому, синхросерия. Синхросигнал может быть внешним или внутренним по отношению к информационным импульсам.

Например в накопителе на магнитной ленте, кроме основной дорожки, часто записывается вспомогательная дорожка, содержащая синхросигналы. Это образец внешней синхронизации.

Для НГМД выделение отдельных синхродорожек на дискете было бы непозволительной роскошью (и так каждый бит на счету). Поэтому применяют специальное кодирование, при котором в самом сигнале содержится как полезная информация, так и синхронизирующие метки. Такой метод носит название «самосинхронизация». Сказанное в полной мере относится к коду МЧМ.

Синхросигнал — это последовательность импульсов, расстояние между которыми равно длительности цифровой позиции Т, а число импульсов равно длине информационного массива. Процесс декодирования заключается в побитовом сравнении информационного сигнала и синхросерии. В любительских контроллерах декодер обычно находится внутри БИС. Это может быть КР1818ВГ93 (в дальнейшем по тексту — ВГ93) или зарубежная БИС i8272A.

В общем случае сигнал воспроизведения и выделенный из него синхросигнал будут иметь фазовые сдвиги. Эти сдвиги являются непредсказуемыми и нежелательными, поскольку из-за них информация может неверно декодироваться. Наличие сдвигов обусловлено массой причин, решающими из которых являются:

- неравномерность углового движения дискеты (биения двигателя и разная скорость вращения ротора у записывающего и воспроизводящего дисководов);

- дефекты магнитной структуры дискеты (местное понижение или повышение амплитуды сигналов);

- фазовые искажения, обусловленные предкомпенсацией сигналов при записи и «сдвигом пиков» выходных сигналов при чтении (эффект межсимвольной интерференции).

На рис. 3 условно показано воздействие фазовых сдвигов на сигнал МЧМ. Теоретически доказано [2], что максимальный временной сдвиг, при котором идеальный контроллер в режиме индивидуальной обработки каждого импульса еще способен правильно декодировать МЧМ-сигнал, составляет +0.25Т.

Штриховкой на рис. 3 отмечены зоны устойчивого декодирования. Их принято называть «окнами детектирования». Если информационный МЧМ-сигнал «выпадает из окна» (точка А), ВГ93 фиксирует ошибку чтения.

Упомянутый теоретический предел «окна детектирования» трудно достижим на практике, поскольку разрешающая способность канала чтения определяется схемотехникой устройств синхронизации. Рассмотрим этот момент подробнее.

СПОСОБЫ РАЗДЕЛЕНИЯ СЧИТЫВАЕМЫХ СИГНАЛОВ

Постановка задачи. Требуется выделить из входного МЧМ-сигнала синхро-серию. Решение поставленной задачи возлагается на специальное устройство, называемое «сепаратор данных» или «выделитель данных» (ВД). Основной критерий эффективности работы — это величина «окна детектирования», чем она больше, тем лучше.

Можно предложить следующую классификацию схем:

ВД-БОС — выделитель данных без обратной связи, выполненный по схеме с непосредственной синхронизацией генератора;

ВД-ЦФС — выделитель данных на основе цифрового фазового синхронизатора, построенный по схеме с отрицательной обратной связью через кольцо ФАПЧ;

ВД-АЦП — выделитель данных с применением аналого-цифрового преобразователя (АЦП).

Схемы первого типа имеют простую структуру. Впрочем, на этом их достоинства заканчиваются. Максимальная разрешающая способность составляет всего лишь половину теоретически достижимого предела, то есть +0,125Т [2].

Схемы второго типа отличаются повышенной сложностью. Они обеспечивают высококачественное выделение синхросигнала при достаточно полном использовании «окна детектирования», в идеале — до величины +0.25Т [2].

Схемы третьего типа сочетают аппаратную простоту и качество, но за счет усложнения алгоритма обработки. Здесь входной МЧМ-сигнал подается через быстродействующий АЦП прямо на вход не менее быстродействующего цифрового сигнального процессора с кэш-памятью. Программа, находящаяся в ПЗУ, виртуально выделяет синхроимпульсы.

Способность запоминания информации в буфере кэш-памяти и позволяет, очевидно, превзойти предел +0.25Т. Это не фантастика, так как теория предсказывает предел для мгновенного отсчета, а ВД-АЦП может оперировать с предыдущей и последующей информацией.

Чтобы не быть голословным, представим ситуацию, когда при одиночном «выпадении» импульса из «окна детектирования» производится математический расчет, и сигнал виртуально «устанавливается» на место. Подобная технология разработана в научно-исследовательском центре компании IBM и носит название PRML (Partial-Response Maximum-Likelihood) — концепция групповой обработки сигналов неполной амплитуды по максимальной вероятности.

В любительских контроллерах применяются схемы первого (ВДБОС) и второго (ВД-ЦФС) типов, как более простые в реализации.

Рассмотрим внутреннее устройство узла чтения на основе схем ВДБОС и ВД-ЦФС.

СТРУКТУРНАЯ СХЕМА КАНАЛА ЧТЕНИЯ

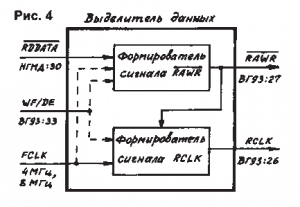

На рис. 4 приведена обобщенная структурная схема канала чтения.

Приведем расшифровку и параметры сигналов для случая метода МЧМ, тактового сигнала CLK частотой 1 МГц на выводе 24 ВГ93:

-RDDATA (ReaD DATA) — «данные чтения с дисковода». Импульсы отрицательной полярности с длительностью 0,15…1,5 мкс и периодом 4; 6; 8 мкс (соответственно, интервалы — Т; 1,5Т; 2Т) [3];

WF/DE (Write Fault/Data Enable) — двунаправленная шина, используемая для обозначения ошибки записи и разрешения выбора данных от компьютера. В режиме чтения этот сигнал имеет «нулевой» уровень, а в режиме записи — «единичный»;

FCLK (Frequency Clock) — «тактовые импульсы». Это сигнал «меандра» внут-реннего кварцевого генератора с частотой 4 или 8 МГц;

-RAWR (RAW Read) — «считывание исходных данных». Импульсы отрицательной полярности с длительностью ‘100…600 нс и периодом 4; 6; 8 мкс [4];

RCLK (Read Clock) — «синхросигнал чтения». Это выделенная из информационного сигнала синхросерия с формой, близкой к «меандру», и периодом, близким к 4 мкс.

Назначение узла чтения состоит в формировании информационного сигнала (-RAWR, вывод 27 ВГ93) и синхросигнала (RCLK, вывод 26 ВГ93). Отличие схем ВД-БОС от схем ВД-ЦФС заключается только в формирователе сигнала RCLK. Пунктирные линии означают необязательные сигналы.

Рассмотрим наиболее типичные схемы, применяемые на практике. Многие из них легко узнаваемы по публикациям в журналах «Радиолюбитель». При анализе не ставится задача критиковать то, что так или иначе прошло «горнило практической обкатки». Поиск «самойсамой» схемы канала чтения в силу объективных причин сейчас не так важен. Пришло время спокойно разобраться и попытаться сделать определенные выводы на будущее.

Для тех, кто далек от темы самодельных компьютеров, думается, будет полезным понимание принципа работы цифровой ФАПЧ. Это может пригодиться в самых разнообразных конструкциях.

ФОРМИРОВАТЕЛЬ СИГНАЛА -RAWR

Самый, простой вариант — вообще обойтись без формирователя (рис.5). Здесь сигнал -RDDATA «по совместительству» является и сигналом -RAWR, проходя напрямую через интерфейсный разъем Х1.

Резистор R1 служит нагрузкой открытого коллектора микросхемы DD1. Его наличие обязательно для всех последующих схем. Номинал

R1 обычно колеблется в пределах от 150…330 Ом (желательно) до 10 кОм. При низких номиналах R1 улучшается согласование волнового сопротивления ленточного кабеля, который находится между дисководом и контроллером. При этом увеличивается крутизна фронта сигнала RDDATA.

Схема, показанная на рис.5 будет работать, если имеется полная уверенность в том, что в конкретном дисководе длительность сигнала -RDDATA (а значит, и -RAWR) не превышает 600 нс. Однако дисковод дисководу рознь. К примеру, согласно техническим данным на НГМД «Электроника МС5305» [3], максимальная длительность -RDDATA составляет 1,5 мкс.

Понятно, что приведенная простейшая схема в контроллерах не прижилась. Очередной шаг напрашивается сам собой — сделать длительность сигнала -RDDATA постоянной. С этим может справиться одновибратор (рис.6).

Длительность выходных импульсов од-новибратора DD2 рассчитывается по приближенной формуле Ти = 0,45*R1*C1. В схемах обычно добиваются значения Ти в пределах 200…300 нс.

Иногда одновибратор строится по схеме формирователя с RC-задержкой (рис.7, [5]).

Сигнал RDD (вывод 23 БИС i8272A) функционально эквивалентен сигналу -RAWR ВГ93. Его длительность определяется цепочкой задержки R1, С1. «Необычный» логический элемент DD1 образован прошивкой программируемой матрицы.

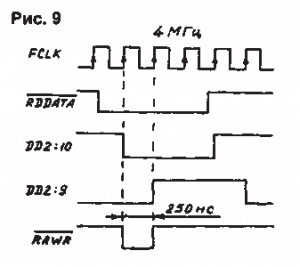

Следует заметить, что в схемах рис. 6, 7 импульсы одновибратора никак не связаны с тактовыми сигналами контроллера. Это вносит дополнительную погрешность в процесс выделения информации. Как следствие, во многих контроллерах схемы были усовершенствованы. В частности, изменить ситуацию помогает привязка сигнала -RDDATA к импульсам синхронизации FCLK (рис.8). Поясняющие временные диаграммы приведены на рис.9.

Длительность сигнала -RAWR строго нормирована величиной 250 нс независимо от периода (4; 6 или 8 мкс). Тактовые импульсы FCLK частотой 4 МГц поступают от внутреннего кварцевого генератора контроллера. Их период определяет длительность сигнала -RAWR.

Сдвиг во времени переднего фронта сигналов -RDDATA и -RAWR (рис.9) не носит принципиального характера, поскольку основная информация переносится периодом следования сигнала.

Существует несколько разновидностей данной схемы, отличающихся типом применяемого логического элемента DD2, вплоть до замены его диодом и резистором. Общим классифицирующим признаком является подача сигнала -RDDATA на D-вход триггера DD1.1.

В схеме на рис.10 сигнал чтения подается на С-вход триггера DD2.1. Логика работы (рис.11) и возможности схемы от этого не меняются. Новизна заключается в применении сигнала WF/DE, блокирующего выдачу импульсов -RAWR в режиме записи информации. Это может понадобиться для корректной работы некоторых схем формирователя сигнала RCLK.

Еще один нюанс, который заслуживает внимания — можно ли «сэкономить» на буферном элементе DD1.1? Не секрет, что D-триггеры ТТЛ-серий ТМ2 очень чувствительны к крутизне фронта импульса на синхровходе. К примеру, согласно техническим условиям, на вход С микросхемы К555ТМ2 желательно подавать сигналы с длительностью фронта и среза не более 15 нc.

Учитывая это, элемент DD1.1 нужен, а вот устанавливаемый в некоторых схемах конденсатор С1 (отмечен пунктиром) — под вопросом. Если С1 удаляет «иголки» сигнала, то стоит вначале попытаться уменьшить номинал резистора R2.

Схемы на рис. 8, 10 относятся к разряду «четырехмегагерцовых»(F CLK). В некоторых контроллерах имеется дополнительно частота 8 МГц. Разработчики не преминули воспользоваться такой возможностью, что позволило уменьшить длительность сигнала -RAWR до 125 нс (рис.12, [6]).

Микросхема DD2 содержит синхронно тактируемые D-триггеры. Временные диаграммы (рис.13) показаны для случая WF/DE=0, то есть для режима чтения.

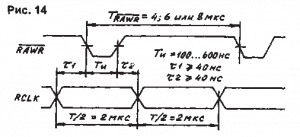

Закономерен вопрос, а зачем вообще нужно уменьшать длительность сигнала -RAWR? Ответ дает рис.14, на котором показаны временные соотношения в «окне детектирования» согласно техническим данным на ВГ93 [4].

Запас «окна детектирования» (ЗП) определяется по формуле ЗП = ±(Т/2 х1 т2 Ти)/2.

Ти — это не что иное как длительность сигнала -RAWR. Если принять т1 = т2 = 40 нс, то для Ти = 125 нс значение ЗП равно +897 мкс (+0.224Т), а для Ти — 250 нс ЗП равно ±835 мкс (+0.209Т). Следовательно, схема на рис.12 теоретически имеет на 7,4 % больший запас «окна детектирования», чем схемы на рис. 8,10, что позволяет ближе подойти к пределу +0.25Т.

Нередко встречаются «гибридные» схемы, у которых -RAWR расщепляется на два сигнала: один из них, длительностью 250 нс, подается на вывод 27 ВГ93; другой, длительностью 125 нс — на схему выделения синхросерии. К чему это приводит, станет ясно при рассмотрении схемотехники формирования сигнала RCLK.

ФОРМИРОВАТЕЛЬ СИГНАЛА RCLK

Изложение данного материала в радиолюбительских статьях обычно сопровождается кратким описанием принципа работы, иногда — графом переходов [6]. Думается, этого недостаточно, ведь за общими фразами не видно физики процесса, а вузовская подготовка имеется далеко не у каждого. Отсюда путаница в понятиях, отсутствие какой-либо классификации.

Попробуем восполнить данный пробел.

СХЕМОТЕХНИКА ВД-БОС

На рис.15, 16 приведены две наиболее простые схемы выделения синхросигнала RCLK из входного информационного сигнала -RAWR.

Формально схемы различаются между собой, во-первых, типом двоичного счетчика DD1, во-вторых, направлением счета импульсов: для К555ИЕ10 — сложение, для К155ИЕ7 — вычитание. Тем не менее, по логике функционирования обе схемы «идентичны».

Для примера рассмотрим принцип работы схемы рис.15 по временным диаграммам рис.17.

Предположим, что вначале входной сигнал -RAWR не содержит фазовых сдвигов. Расстояние между импульсами в точности равно 4 (6, 8) мкс, длительность — 250 нс (рис.176).

В момент времени «А» в счетчик DD1 по фронту сигнала FCLK со входов D8, D4, D2, D1 записывается двоичное число «0101» (десятичное «5»). Далее состояние счетчика каждый раз увеличивается на единицу по фронту тактовых импульсов FCLK.

В момент прихода следующего импульса -RAWR (точка «В») состояние счетчика должно измениться с «4» на «5», что как раз совпадает с числом, принудительно вводимым со входов D8, D4, D2, D1. Таким образом, при «идеальном» сигнале -RAWR счетчик делит частоту FCLK ровно на 16, и на выходе сигнал RCLK (рис.17в) представляет собой «меандр».

Импульсы -RAWR располагаются примерно посредине «окна детектирования» на расстоянии t2 от левого края и t1 от правого края. Созданы все условия для безошибочного выделения информации.

Аналогичные рассуждения можно привести для случая Т=6 мкс, при этом в счетчик в точке «В» записывается двоичное число «1101» (десятичное «13») и т. д. Случай Т=8 мкс полностью совпадает с Т=4 мкс.

Далее, предположим, что в результате действия помех первый импульс -RAWR получил фазовый сдвиг +0,125Т, а второй импульс — −0,125Т (рис.17г). В точке «С» вместо числа «7» в счетчик будет записано число «5», то есть происходит добавление двух лишних импульсов. В точке «D» — наоборот, происходит вычитание четырех импульсов.

В результате сигнал -RAWR все еще находится внутри «окна детектирования», но на самом пределе у левого края (t3). Например если сдвинуть точку «D» влево на очередные 250 нс, то временные соотношения для ВГ93 (рис.14) уже перестанут выполняться.

Рассмотрим зеркальный вариант, когда первый импульс -RAWR получает отрицательный, а второй импульс — положительный фазовый сдвиг. Оказывается, что в этом случае запас «окна детектирования» будет несколько меньше —+0,062Т…-0,125Т.

Таким образом, для схемы на рис.15 усредненный ЗП = +0,109Т при теоретическом пределе +0,125Т.

В зависимости от типа формирователя -RAWR, может иметь место взаимное смещение во времени сигналов -RAWR и FCLK, иногда регулируемое конденсатором. Данный факт следует учитывать при анализе временных диаграмм конкретных схем.

Что будет, если в счетчик вместо числа «5» вводить другое число? Вследствие асимметрии, импульс -RAWR сместится к краю «окна детектирования», ухудшая тем самым условия выделения данных. Оптимальное число К можно вычислить из логически понятного соотношения:

8-К = К-1, откуда К=4,5. При этом числа «8» и «1» обозначают максимально возможные состояния счетчика соответственно слева и справа от точки «А» на диаграмме рис.17б.

Теперь становится ясно, почему вывод 3 микросхемы DD1 иногда подключают к общему проводу (рис.15, пунктир), обеспечивая ввод числа «0100» или «4». При этом возможности устройства остаются прежними.

Блокировка канала чтения по сигналу WF/DE в схеме рис.16 не нужна, если выходы счетчика не используются для формирования внутренних сигналов.

На рис.18 изображена более сложная разновидность схем ВДБОС.

Тактовая частота FCLK увеличена до 8 МГц, а длительность сигнала -RAWR уменьшена до 125 нc, что должно давать определенные преимущества. На временных диаграммах (рис. 19) подробно разрисованы состояния счетчика DD1 при отсутствии фазовых сдвигов (рис.196, в, г) и при их наличии (рис.19д, е, ж).

Запись числа «6» в счетчик К155ИЕ7 происходит не по фронту FCLK, как в К555ИЕ10, а низким уровнем сигнала -RAWR. Триггер DD2 включен по схеме делителя частоты на 2.

Запас «окна детектирования» составляет в среднем ±0,117Т, что на 7,4 % больше, чем в схемах рис 15,16. Оптимальное число К равно 6,5; то есть или «6», или «7». Иногда встречаются схемы, где вводится число «5». Их желательно доработать. Можно ли улучшить характеристики системы при переходе к частоте FCLK 16 МГц? Ответ отрицательный, поскольку значение t3 на диаграммах станет менее 40 нс, что. недопустимо для ВГ93. Дальнейшие усовершенствования требуют кардинального изменения алгоритма.

ИНФОРМАЦИОННАЯ МОДЕЛЬ

После того как «на пальцах» удалось разобрать принцип работы выделителя данных, перейдем к обобщениям. В последующих рассуждениях будут встречаться абстрактные понятия — это своеобразная реакция человека на непривычный «цифровой способ мышления компьютера».

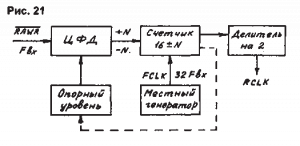

Логическую структуру схем на рис.15,16 удобно представить как рис.20, а схемы на рис.18 — как на рис.21.

Сигнал -RAWR поступает на цифровой фазовый детектор (ЦФД). Его роль выполняет цепь принудительного ввода кода (D8, D4, D2, D1) счетчиков К555ИЕ10 или К155ИЕ7. Опорный уровень (Fbx) — это не что иное как аппаратно задаваемый код, например число «0110» («6») в схеме на рис.18.

ЦФД сравнивает «местоположение» на временной оси приходящего сигнала -RAWR с опорным числом и, при наличии фазовых сдвигов, добавляет (+N) или вычитает (-N) соответствующее число импульсов, поступающих на счетчик. Тем самым производится фазочастотное регулирование компенсационного типа. Этот процесс отчетливо виден на рассмотренных ранее временных диаграммах.

В случае N=0 частота FCLK местного кварцевого генератора делится в счетчике ровно на 16. Период сигнала RCLK равен 1/FBX при оптимальном расположении «окна детектирования».

В схеме на рис.21 частота FCLK увеличена в 2 раза, поэтому на выходе применяется дополнительный делитель частоты на 2.

Обе рассмотренные структурные схемы не имеют функциональных обратных связей. Местная обратная связь Q8-D8 (рис.15) не учитывается. Опорный уровень задан жестко, поэтому система является простым синхронизатором, любой фазовый сдвиг входного сигнала приводит к такому же по величине фазовому сдвигу выходного сигнала.

Графическая интерпретация процесса приведена на рис.22, который составлен на основании табл. 1.

Табл.1

| Состояние счетчика | Число N | Фазовый сдвиг DT | ||

|---|---|---|---|---|

| предыдущее | последующее | |||

| Точка «C» на рис.17г | 4 | 5 | 0 | 0 |

| 5 | 5 | +1 | +(1/16)T | |

| 6 | 5 | +2 | +(2/16)T | |

| 7 | 5 | +3 | +(3/16)T | |

| Точка «D» на рис.17г | 4 | 5 | 0 | 0 |

| 3 | 5 | −1 | -(1/16)T | |

| 2 | 5 | −2 | -(2/16)T | |

| 1 | 5 | −3 | -(3/16)T | |

| 0 | 1 | −4 | -(4/16)T | |

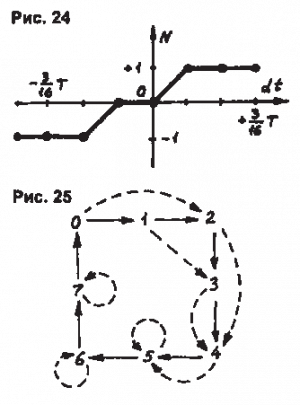

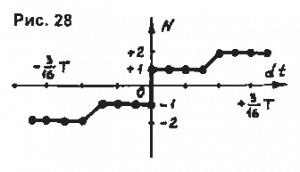

Для ВД-БОС линия управления построена по точкам и проходит под углом 45 градусов через начало координат (линия 1).

Предположим, что можно произвольно изменять угол наклона прямой. Для этого необходимо ввести обратную связь, как показано на рис.20, 21 пунктиром.

Если линия управления будет проходить вблизи вертикальной оси (линия 2), то система станет очень неустойчивой. Достаточно пару раз подряд появиться фазовому сдвигу (1/16)Т одного и того же знака, и импульс -RAWR выйдет за пределы «окна детектирования». Налицо образец положительной обратной связи.

Логично предположить также образование отрицательной обратной связи и, как следствие, более стабильную работу (линия 3).

Действительно, «разумная» система «сообразила» бы, что вслед за небольшим положительным фазовым сдвигом по теории вероятности последует небольшой отрицательный фазовый сдвиг. Менять значение коэффициента деления счетчика при малых возмущениях, очевидно, нецелесообразно. Да и при больших фазовых сдвигах поддаваться панике не стоит скорее всего, это одиночное искажение, после чего система опять вернется в исходное состояние. Следовательно, при больших возмущениях фазовый сдвиг выходного сигнала должен измениться больше, чем при малых возмущениях, но меньше, чем в случае ВД-БОС.

Таким образом, получилось словесное описание инерционной системы синхронизации с подстройкой фазы через кольцо ФАПЧ [2].

Цифровая ФАПЧ в схеме выделителя данных имеет свою специфическую структуру. Чтобы избежать путаницы в терминологии, обычно такие системы называют ЦФС — цифровыми фазовыми синхронизаторами [7]. В некоторых публикациях подчеркивается, что ЦФС — это системы авторегулирования на основе анализа фазовых соотношений между сигналами.

Табл. 2

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00h: | 08 | 00 | 00 | 00 | 14 | 00 | 00 | 00 | 10 | 00 | 00 | 00 | 18 | 00 | 00 | 00 |

| 10h: | 0C | 00 | 00 | 00 | 14 | 00 | 00 | 00 | 10 | 00 | 00 | 00 | 1C | 00 | 00 | 00 |

Табл. 3

| P | Q8 | Q4 | Q2 | Q1 | A4 | A3 | A2 | A1 | A0 | Адрес РЕ3 | Код РЕ3 | D8 | D4 | D2 | D1 | M | N |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00h | 08h | 0 | 0 | 1 | 0 | 2 | −1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 10h | 0Ch | 0 | 0 | 1 | 1 | 3 | −1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 08h | 10h | 0 | 1 | 0 | 0 | 4 | −1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 18h | 10h | 0 | 1 | 0 | 0 | 4 | 0 |

| 4 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 04h | 14h | 0 | 1 | 0 | 1 | 5 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 14h | 14h | 0 | 1 | 0 | 1 | 5 | +1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0Ch | 18h | 0 | 1 | 1 | 0 | 6 | +1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1Ch | 1Ch | 0 | 1 | 1 | 1 | 7 | +1 |

Условные обозначения:

- Р — предшествующее состояние счетчика;

- М — последующее состояние счетчика;

- N=P-M+1 — число импульсов компенсации.

С другой стороны, термин «узел чтения на основе цифровой ФАПЧ» прочно вошел в лексикон радиолюбителей, и было бы несправедливо лишать их возможности использовать свой сленг.

СХЕМОТЕХНИКА ВД-ЦФС

Возвратимся к графику закона регулирования ЦФС (рис.22). Линия регулирования с отрицательной обратной связью (линия 3) показана в качестве абстрактного примера. На практике ее форма больше напоминает кусочно-линейную функцию.

Какую именно — это и предстоит выяснить для каждой конкретной схемы.

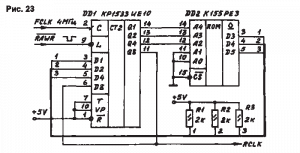

На рис.23 представлена одна из самых простых реализаций ВДЦФС. Схема очень похожа на рис.15 при добавлении ПЗУ DD2 К155РЕЗ (таблица прошивки представлена в табл.2) и нагрузочных резисторов R1…R3. Конструктивная доработка заключается в напайке микросхемы DD2 поверх DD1 прямо на печатной плате контроллера.

Обратная связь вводится по трем разрядам счетчика — D1, D2, D4. ПЗУ выступает в роли преобразователя кода, что наглядно видно из табл.3.

Теперь легко составить «фазовый портрет» схемы (рис.24), а также граф переходов (рис.25). Для удобства рассматриваются числа 0…7, оставшиеся числа 8…15 имеют аналогичную структуру. На графике можно выделить три реакции на возмущение: +1, 0, −1, а также две устойчивые точки со значением N=0.

Временные диаграммы (рис.26) показывают увеличение «окна детектирования» до +0,187Т, что на 71 % больше, чем в схеме-прототипе. Налицо полезность ВД-ЦФС.

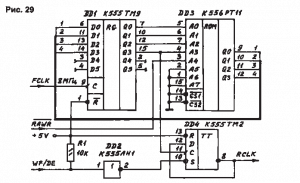

В «8-мегагерцовых» схемах также возможно введение цифровой обратной связи (рис.27, [6]).

Роль преобразователя кодов возложена на сумматор DD3. Счетчик DD1 работает на сложение, триггер DD4 делит частоту на 2. Анализируя логические состояния, нетрудно составить характеристику регулирования (рис.28). Ее особенностью является сжатый в два раза масштаб по оси N, увеличенное количество точек, а также четыре варианта реакции на возмущение: −2, −1, +1, +2.

Устойчивых точек на графике нет. Это означает, что в установившемся режиме при идеальном -RAWR система будет постоянно колебаться между точками +1 и −1 на оси N.

Табл. 4

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00h: | 01 | 01 | 02 | 03 | 03 | 04 | 05 | 06 | 0B | 0C | 0D | 0E | 0E | 0F | 00 | 01 |

| 10h: | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 00 |

Те, кому удобнее ориентироваться по графу переходов, могут уточнить его рисунок, приведенный в [6], добавлением пунктирной связи между состояниями «15» и «1». Точно такие же графы переходов имеют две схемы, приведенные в [8]. Запас «окна детектирования», вопреки ожиданиям, остается таким же, как и в предыдущей «4-мегагерцовой» схеме и составляет +0,187Т. Это следствие излома характеристики регулирования.

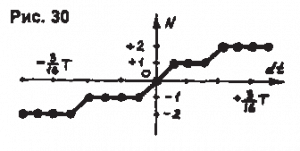

Изящное решение данной проблемы предложено в схеме на рис.29, в которой применяется программируемая матрица DD3 (табл.4).

Микросхема DD1 не может работать отдельно от DD3. Их связка образует оригинальную пересчетную схему. При единичном уровне сигнала -RAWR используются коды прошивки 10h…1Fh, при этом устройство превращается в обычный суммирующий счетчик. При нулевом уровне -RAWR (коды 00h…0Fh) вносится рассогласование с добавлением или вычитанием N импульсов.

«Фазовый портрет» (рис.30) имеет 5 реакций на возмущение и одну устойчивую точку (N=0), в связи с чем усредненный запас «окна детектирования» расширяется до +0,208Т.

Небольшой нюанс. Высокие параметры схем ВД-ЦФС обеспечиваются при соблюдении ряда условий. Во-первых, перепад из «нуля» в «единицу» сигнала FCLK должен происходить ближе к середине импульса -RAWR, как на рис.19. Во-вторых, длительности сигналов -RAWR, поступающих на ВГ93 и на формирователь RCLK, должны быть одинаковы и составлять 125 нc. Расширение -RAWR (вывод 27 ВГ93) до 250 нc автоматически сужает запас «окна детектирования».

В практических схемах эти условия часто не выполняются, что не позволяет полностью использовать возможности схем ВД-ЦФС.

Все вышеизложенные рассуждения о ВД-ЦФС справедливы при равновероятном распределении мгновенных фазовых сдвигов. Более естественным выглядит предположение, что плотность вероятности имеет колоколообразную форму, наподобие Гауссовой кривой. «Ширина» колокола разная у разных дисководов. Кроме того, возможна асимметрия фазовых сдвигов из-за, например, постоянного смещения угловой скорости вращения ротора двигателя НГМД в какую-либо сторону.

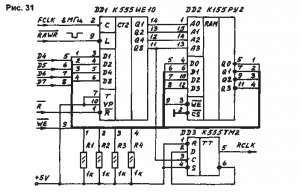

Приспособиться к реалиям жизни позволяет динамическая обратная связь, при которой характеристика управления может оперативно меняться программным способом (рис.31, компьютер «ATM-TURBO-2» [9]). Здесь вместо ПЗУ применяется ОЗУ К155РУ2 (DD2), загрузка которого происходит через шину данных компьютера D4…D7 по сигналу -WE. При этом обнуляется счетчик DD1 (-R), блокируется сигнал -RAWR, а вместо сигнала FCLK на схему подаются специальные импульсы перебора адресов А0…A3. Записываемые данные определяют угол наклона «фазового портрета», его смещение и величину.

При инициализации компьютера в микросхему DD2 загружается начальная характеристика, например аналогичная рис.30. Если при чтении дискеты встречаются ошибки,

то в DD2 заносятся другие коэффициенты, после чего процесс чтения повторяется. И так продолжается до тех пор, пока подбором характеристик не удается прочитать данные. В противном случае принимается решение о фатальной ошибке.

Компьютер не может прочитать информацию из ОЗУ контроллера, поэтому, во избежание сбоев, желательно при каждом новом чтении дискеты вновь загружать начальную характеристику.

Табл. 5

| Схема | Длительность -RAWR | FCLK | Максимальный фазовый сдвиг |

|---|---|---|---|

| Рис.5 | 150…1500нс | отсутствует | ±0,052Т |

| Рис.6 | 200…300 нс | отсутствует | ±0,177Т |

| Рис.8,10 | 250 нс | 4 МГц | ±0,209Т |

| Рис.12 | 125 нс | 8 МГц | ±0,224Т |

Табл. 6

| Схема | Тип | FCLK | Усредненный фазовый сдвиг | Теоретический фазовый сдвиг |

|---|---|---|---|---|

| Рис.15,16 | ВД-БОС | 4 МГц | ±0,109Т | +0.125Т |

| Рис.18 | ВД-БОС | 8 МГц | ±0,117Т | ±0,125Т |

| Рис.23 | ВД-ЦФС | 4 МГц | +0,187Т | +0.25Т |

| Рис.27 | ВД-ЦФС | 8 МГц | ±0,187Т | ±0,25Т |

| Рис.29 | ВД-ЦФС | 8 МГц | ±0,208Т | ±0,25Т |

| Рис.31 | ВД-ЦФС (динам.) | 8 МГц | в зависимости от алгоритма | ±0,25Т |

К сожалению, большие потенциальные возможности динамической ЦФС в компьютере «ATM-TURBO-2» лишь декларируются, поскольку нет соответствующей программной поддержки для компьютеров, выпущенных с 1993 по 1995 г. По-хорошему, драйвер динамического чтения следовало бы разместить прямо в ПЗУ компьютера. Очевидно, разработчик не стал «использовать» все 100 % возможностей схемы ВД-ЦФС, и отложил функцию динамического улучшения чтения на будущие версии программного обеспечения.

В промышленных контроллерах на базе ВГ93 (ЭВМ «Электроника МС0585») в канале чтения применяется сложная аналоговая ФАПЧ.

ОБОБЩЕНИЕ РЕЗУЛЬТАТОВ

1. В формирователе сигнала RAWR должна осуществляться жесткая синхронизация сигнала -RDDATA с тактовыми импульсами контроллера 4 или 8 МГц. Для «восьмимегагерцовых» схем следует применять быстродействующую логику, например микросхемы серий КР1531, КР531 и т. д.

2. Длительность сигнала -RAWR должна быть не менее 100 нс. Рекомендуемый ряд: 125 нс, 187 нс, 250 нс. При переходе от 250 нс к 125 нс теоретический запас «окна детектирования» увеличивается на 7,4 %. Противопоказанием к уменьшению длительности -RAWR могут быть: неудачная разводка проводников печатной платы, низкое быстродействие микросхем, нестандартный экземпляр ВГ93.

3. Желательно, чтобы входной сигнал -RDDATA поступал в схему через буферный элемент типа К555ТЛ2, имеющий характеристику триггера Шмитта. Резистор между сигналом -RDDATA и шиной +5 В должен иметь достаточно низкое сопротивление — порядка 330 Ом.

4. Схемы ВД-ЦФС, по сравнению с ВД-БОС позволяют получить выигрыш по запасу «окна детектирования» на 71 %, что значительно повышает качество считывания информации с дискет. При этом уменьшение длительности сигнала -RAWR на улучшение чтения влияет гораздо меньше (7,4 %).

5. В табл.5, 6 приведены сравнительные параметры рассмотренных в статье схем. Значения частот FCLK в схемах формирователя сигнала -RAWR и формирователя сигнала RCLK должны совпадать.

6. Колонка «усредненный фазовый сдвиг» в табл.6 позволяет лишь качественно сравнивать схемы между собой. Математическое моделирование (листинг 1) показывает, что при равновероятных сдвигах от 0 до +0,187Т (±750 нс) схема на рис.15 будет в среднем выдавать одну ошибку на каждые 5, а схема на рис.23 — на каждые 25 импульсов -RDDATA.

Листинг 1

10 REM Моделирование работы выделителя данных 20 LET a$ = "ВД-БОС:" 30 LET s = 0: LET b = 0: FOR i = 1 TO 7 40 READ n: REM Сдвиг фазы предыдущего импульса 50 FOR j = -3 TO 3: REM Сдвиг фазы последующего импульса 60 IF j n >3 OR j n < -4 THEN LET s = s + 1 70 LET Ь b + 1: NEXT j: NEXT i 80 PRINT aS; "Одна ошибка на"; INT(b / s + .5); "импульсов" 90 IF a$ = "ВД-ЦФС: " THEN STOP 100 LET aS = "ВД-ЦФС: ": GOTO 30 110 REM Ввод коэффициентов N "фазового портрета" 120 DATA -3,-2,-1,0,1,2,3: REM ВД-БОС, рис.15,22 130 DATA -1,-1, 0,0,1,1,1: REM ВД-ЦФС, рис.23,24

7. Характеристика регулирования схем ВД-ЦФС должна быть по возможности плавной, монотонной и иметь хотя бы одну устойчивую точку N=0. Угол наклона характеристики определяет большую или меньшую инерционность системы регулирования (цифровой фильтр). Например приближение характеристики к горизонтальной оси эквивалентно увеличению постоянной времени и наоборот.

8. В практических схемах ВДЦФС вертикальный размах значений N для характеристики управления не выходит за пределы +1 для «четырехмегагерцовых» и +2 для «восьмимегагерцовых» схем. В качестве образца могут служить рис.24, 30.

9. Оптимальной характеристики ВД-ЦФС на все случаи жизни не существует, для каждого дисковода — по-своему. Если в схемах рис.23 и рис.29 микросхемы ПЗУ установлены на панельках, можно осуществить экспериментальный подбор из нескольких версий с разными прошивками.

10. Наибольшими потенциальными возможностями обладает схема динамической ВД-ЦФС (рис.31). Программная поддержка для нее должна резидентно входить в состав оболочек типа HONEY COMMANDER («ZX-SPECTRUM»). Очень перспективно применение алгоритмов нечеткой логики.

11. Схемы ВД-БОС изначально нельзя было применять в отечественных контроллерах дисководов. НГМД типа «Электроника МС5305», согласно формуляру [3], гарантирует местоположение сигнала -RDDATA в пределах +700 нс от номинального положения. Это эквивалентно фазовому сдвигу +0.175Т. Следовательно, применение схемы ВД-БОС, обеспечивающей в лучшем случае +0.117Т, является конструктивной ошибкой. Разумеется, случаи хорошей работы не исключаются, но они будут опираться или на заводской технологический запас, или на прецизионную юстировку механики, или на японское качество дисководов ТЕАС. Если бы разработчики домашних компьютеров сразу применили схемы ВД-ЦФС с запасом «окна детектирования» +0.208Т, нареканий на некачественное чтение дискет было бы гораздо меньше.

Литература

- Рюмик С. Контроллер дисководов. Канал записи. — Радиолюбитель. Ваш компьютер, 1998, NN10-12; 1999, N1.

- Рыжков В. А. и др. Внешние запоминающие устройства на магнитном носителе. — М.: Энергия, 1978.

- Накопитель на гибких магнитных дисках «Электроника МС5305». Формуляр ЛУКФ.467616.001 ФО.

- Микросхема КР1818ВГ93. Технические условия 6К0.348.877-08ТУ.

- Щелкунов Н., Дианов А. Организация контроллеров ГМД. — Микропроцессорные средства и системы, 1990, N4, С.70.

- Nemo. Контроллер дисковода для компьютера «KAY-256». — Радиолюбитель, 1995, N3, Сб.

- Системы фазовой синхронизации с элементами дискретизации/ Под ред. В. В. Шахгильдяна. — М.: Радио и связь, 1989.

- Зелинский В. Доработка контроллера дисковода. — Радиолюбитель. Ваш компьютер, 1997, N7, С.28.

- Морозов А. Персональный компьютер «ATM-TURBO-2». — Радиолюбитель, 1993, N1-6.