ЮТ-88/ЮТ-УМ 06-89/Модуль дополнительного ОЗУ

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Автор: В. БАРТЕНЕВ Источник: http://retro.h1.ru/UT88/Memory/Memr.php |

Тема сегодняшнего разговора — блок памяти «ЮТ-88» емкостью 64 Кбайт, который позволит вам использовать все множество программ, написанных для «Микро-80», «Радио-86РК» и «Специалиста». Выполнен он на микросхемах ОЗУ динамического типа.

В динамическом ОЗУ используются интегральные микросхемы, в которых хранение информации в матрице ячеек памяти определяется наличием заряда в запоминающих емкостных элементах. Однако если к этим элементам долгое время не обращаться, то за счет тока утечки информация может стереться. Для предотвращения этого эффекта необходимо периодически считывать информацию из каждой ячейки памяти. При этом усилитель считывания автоматически восстанавливает заряд на запоминающих емкостях, обеспечивая сохранность данных. Такой режим работы динамического ОЗУ называется регенерацией.

В динамическом ОЗУ каждый столбец матрицы ячеек памяти имеет свой усилитель считывания, поэтому процедуру регенерации можно выполнять одновременно для всей строки. Ограниченное число выводов на корпусе микросхем ОЗУ потребовало применения мультиплексирования режима выбора адреса, при котором для выбора строк и столбцов матрицы ячеек памяти используются одни и те же адресные входы.

В начале производится выбор строк путем подачи соответствующего кода на адресные входы А0… А7 и нулевого уровня на вход сигнала выборки строк RAS. При этом код строки записывается в адресный регистр и с помощью дешифратора строк выбирается регенерируемая строка. Для надежного хранения информации необходимо производить режим регенерации по всему диапазону строк с периодом не более 2 мс.

Существует несколько стандартных алгоритмов процедуры регенерации. В частности, можно до начала регенерации приостановить работу микропроцессора, воздействуя на его вход ГТ. Получив ответный сигнал ОЖ, можно произвести цикл регенерации. В описываемом модуле динамического ОЗУ использован другой путь: регенерация происходит не в моменты остановки микропроцессора, а в интервале времени между двумя любыми циклами обращения к памяти. Минимальный цикл между обращениями к памяти для микропроцессоре КР580ВМ80А равен трем тактам (трем периодам тактовой синхросерии Ф2). При используемой в компьютере частоте кварцевого резонатора 16МГц длительность такта составляет 0,565 мкс. Для реализации «прозрачной» регенерации ОЗУ в этом случае имеется достаточно времени даже при использовании микросхем К565РУ5Д с временем цикла 450 нс.

Такой режим регенерации позволяет организовать обмен данными в синхронном режиме, не требует информации о состоянии микропроцессора и, главное, исключает простой микропроцессора. В режимах чтения и записи регенерация ячеек памяти подключенных к выбранной строке, осуществляется автоматически. В режиме чтения на вход микросхем WE подается уровень логической единицы, а в режиме записи — уровень логического нуля, после чего на входы А0…А7 подается код столбца и с некоторой задержкой нулевой уровень на вход выбора столбца CAS. С помощью дешифратора столбцов определенная шина столбца через соответствующий ключ выборки подключается к шине данных, осуществляя запись или считывание информации в выбранной ячейке памяти.

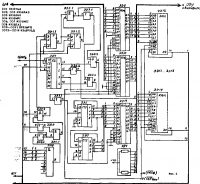

Электрическая схема модуля динамического ОЗУ изображена на рисунке 2. Модуль включает в себя, контроллер ОЗУ, реализованный на микросхемах DD1—DD1.1, и основной блок ОЗУ объемом 64 Кбайта, на микросхемах DD12—DD19, перекрывающей адресное пространстве 0000Н—FFFFH. Модуль динамического ОЗУ может быть использован как с процессорным модулем, так и совместно с дисплейным модулем.

Поскольку в процессорном модуле и в дисплейном модуле могут использоваться свои ПЗУ—ОЗУ, в модуле динамического ОЗУ имеется 8-входовая схема (DD8) блокировки запросов обращения к модулю динамического ОЗУ, В частности, при работе модуля динамического ОЗУ только с микроЭВМ минимальной конфигурации, на входы блокировки следует подключить сигналы выборки адресного пространства 0000Н—0FFFH, а на входы выборки кристалла микросхем ОЗУ процессорного модуля КР541РУ2 подать сигналы логической единицы. В этом случае доступная область динамического ОЗУ будет составлять 60 Кбайт от 1000Н до FFFFH.

При подключении дисплейного модуля на входы блокировки подключают сигналы выборки адресного пространства 0000Н—0FFFFH, E000H—EFFFH и F000H— FFFFH. Работая с монитором в F800H—FFFFH, можно не входы выборки кристалла микросхем ПЗУ КР556РТ5 подать сигналы логической единицы, а с входа блокировки отключить сигналы выборки адресного пространства 0000Н— 0FFFH.

В такой конфигурации доступная область динамического ОЗУ составит 56 Кбайт от 0000Н до 0FFFH. Сигналы выборки адресных пространств низкого уровня препятствуют формированию в триггере DD1 сигнала длительностью, определяющей временной интервал обращения к ОЗУ. При этом модуль ОЗУ находится в режиме регенерации.

Контроллер ОЗУ состоит из мультиплексора адреса, реализованного на микросхемах ПЗУ DD9—DD11, счетчика адреса регенерации на микросхемах DD6 и DD7 (К155ИЕ5), схемы управления на регистре DD4 (К155ИР1), триггерах DD1 и логических микросхемах DD2, DD3, DD5. При поступлении сигналов ЧТЗУ или ЗПЗУ по фронту импульса Ф2ТТЛ с помощью триггеров DD1 на выходе схемы «2И-НЕ» (DD 2.1). Формируется импульс, длительность которого определяет цикл обращения к ОЗУ. С помощью регистра сдвига (DD4), который тактируется импульсами частотой 16МГц и импульсами Ф2ТТЛ, подаваемыми на входы регистра, сдвига, формируются импульсы временных шкал. После объединения с импульсом обращения к ОЗУ они дают управляющие сигналы CAS, сигналы подключения адресов строк и столбцов (для мультиплексоров) и сигналы подключения адреса регенерации.

После завершения обмена данными модуль ОЗУ переходит в режим регенерации с одним сигналом RAS, формируемым инвертированием одного из импульсов временных шкал (вывод 12DD4). Содержимое микросхем ПЗУ, используемых в качестве мультиплексоров (DD9— DD11), следующее:

0000 00 01 02 03 04 05 06 07 08 09 0А 0В 0С 0D 0Е 0F 0010 10 11 12 13 14 15 16 17 18 19 1А 1В 1C 1D 1E 1F 0020 20 21 22 23 24 25 26 27 28 29 2A 2В 2С 20 2E 2F 0030 30 31 32 33 34 35 36 37 38 39 ЗА 3В ЗС 3D ЗЕ 3F 0040 40 41 42 43 44 45 46 47 48 49 4А 4В 4С 4D 4Е 4F 0050 50 51 52 53 54 55 56 57 58 59 5А 5В 5С 5D 5Е 5F 0060 60 61 62 63 64 65 66 67 68 69 6А 6В 6С 6D 6Е 6F 0070 70 71 72 73 74 75 76 77 78 79 7А 7В 7С 7D 7Е 7F 0080 80 81 82 83 84 85 86 87 88 89 8А 8В 8С 8D 8Е 8F 0090 90 91 92 93 94 95 96 97 98 99 9А 9В 9С 9D 9Е 9F 00А0 А0 А1 А2 A3 А4 А5 А6 А7 А8 А9 AA AB AC AD AE AF 00B0 B0 B1 B2 ВЗ В4 В5 В6 87 В8 В9 ВА ВВ ВС BD BE BF 00С0 С0 С1 С2 СЗ С4 С5 С6 С7 С8 С9 СА СВ СС CD СЕ CF 00D0 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 DA DB DC DD DE DF 00E0 E0 E1 E2 E3 E4 E5 E6 E7 Е8 Е9 EA ЕВ EC ED ЕЕ EF 00F0 F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

В остальных ячейках находятся значения FF.

После подключения модуля ОЗУ к микроЭВМ минимальной конфигурации вначале отключают провод от вывода 8 микросхемы DD8, переводя работу модуля ОЗУ только в режим регенерации. С помощью осциллографа проверяют наличие на выводах микросхем ОЗУ DD12—DD19 адресов регенерируемых строк, импульсов RAS, затем с помощью простейшей программы, записанной в области статистического ОЗУ процессорного модуля директивной «1» и запущенной директивой «6».

С000 3E 22 С002 32 00 40 С005 ЗА 00 40 С008 СЗ 00 С0

добиваются появления на выходе логического элемента DD1 импульса обращения к ОЗУ, а на выводе 15 микросхем ОЗУ сигнала CAS.

Затем с помощью директивы «0» и «5» записывают и считывают в ОЗУ данные. С помощью подпрограммы монитора копирования данных заносят данные из одной области ОЗУ в другую и с помощью директивы «8» вычисляют контрольные суммы обеих областей. В исправном ОЗУ эти области должны иметь одинаковые контрольные суммы.

А. БАРТЕНЕВ, инженер

Отсканировано с журнала «ЮТ для умелых рук» № ? 1989 г.

Отредактировано Лесных Ю. И. 1999 г.