Радио-86РК/Радио 07-88/Еще раз о наладке

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Автор: Д. ГОРШКОВ, Г. ЗЕЛЕНКО. Ю. ОЗЕРОВ Источник: http://retro.h1.ru/RK86/Naladka/Test.php |

Как показал опыт повторения компьютера «Радио-86РК», большинство машин начинает работать сразу после включения питания. Однако если этого не произошло, то «оживление» компьютера становится весьма трудоемкой задачей, поскольку методика, предложенная в июльском номере журнала за 1986 г., по отзывам читателей, оказалась малоэффективной. В настоящее время разработана новая методика, хорошо зарекомендовавшая себя при отлаживании большого числа компьютеров.

Перед включением компьютера «Радио-86РК» следует проверить правильность подключения источников питания. Особое внимание при этом необходимо обратить на подводку напряжения −5В к микропроцессору и микросхемам памяти К565РУ3. Отсутствие этого напряжения обычно приводит к выходу их из строя.

После контроля напряжений питания на всех микросхемах можно приступать к проверке работы тактового генератора КР580ГФ24 (D1). На его выходе OSC должны присутствовать импульсы частотой 16 МГц, скважностью 2 и амплитудой около 2В. При их отсутствии необходимо отсоединить вывод OSC от монтажа и снова проверить наличие сигнала на нем, появление сигнала OSC свидетельствует о дефектах монтажа или микросхем К155ИЕ4 (D3) и К155ИР1 (D16). Отсутствие сигнала OSC в этом случае свидетельствует о неисправности кварцевого резонатора или микросхемы тактового генератора. Для проверки работоспособности генератора вместо кварцевого резонатора к его входам X1 и Х2 временно подключают конденсатор емкостью 10…15 пФ. Кроме этого, необходимо проверить наличие других сигналов, формируемых тактовым генератором. На выходе Ф1 должен присутствовать периодический сигнал частотой 1,7(7) МГц скважностью 9 и амплитудой 12В на выходе Ф2 — периодический сигнал с такой же частотой и амплитудой, но скважностью 9/4, на выходе Ф2 TTL — сигнал, аналогичный по форме Ф2, но с амплитудой 5В. При отсутствии какого-либо из этих сигналов необходимо отсоединить соответствующий вывод микросхемы D1 от монтажа, и если сигнал при этом появляется, то искать неисправность следует либо в монтаже, либо в микросхемах, на входы которых этот сигнал поступает. Полезно также проверить наличие высокого уровня на выходе RDY тактового генератора.

Далее проверяют появление положительных импульсов длительностью 2-5 мс на выходе RES тактового генератора при каждом нажатии кнопки «СБРОС» (которую нажимают не чаще одного раза в секунду). Если импульсы не появляются или их длительность превышает 5 мс, необходимо проверить работу узла формирования сигнала сброса (С1, С2, R1, R2, V1). При нажатии кнопки «СБРОС» он должен формировать на входе RESIN микросхемы КР580ГФ24 отрицательный пилообразный импульс. Наиболее часто причиной его отсутствия является неверная полярность включения диода V1. При использовании кнопки с большим дребезгом контактов сигнал на входе RESIN может иметь несколько пиков, работоспособность РК при этом сохраняется.

Теперь можно подключить к тактовому генератору устройство пошаговой работы («пошагиватель»), схема и подключение которого приведены в упомянутом номере журнале.

«Пошагиватель» позволяет проводить отладку компьютера в статическом режиме, то есть во время выполнения каждого машинного цикла переводить микропроцессор в состояние ожидания до следующего нажатия кнопки «ШАГ». Находясь в состоянии ожидания, микропроцессор поддерживает сигналы на шинах неизменными, поэтому появляется возможность легко проконтролировать уровни этих сигналов, например, осциллографом или подключив к шине данных через какой-либо шинный формирователь (например, КР580ВА87), светодиоды через токоограничительные резисторы сопротивлением 300 0 м.

Для дальнейшей наладки РК необходимо также вместо ПЗУ с управляющей программой МОНИТОР (D17) поместить в панель ПЗУ с кодами отладочной программы, текст которой приведен в табл. 1. При выполнении программы в пошаговом режиме состояние сигналов на линиях шин адреса, данных и управляющих сигналов должно соответствовать приведенным в табл.2.

ТАБЛИЦА 1. ;Программа для наладки РАДИО-86РК C000 = VG75 EQU 0C000H E000 = VT57 EQU 0E000H 8000 = VV55 EQU 8000H F800 ORG 0F800H F800 C303F8 JMP BEGIN ;Инициализация KP580BB55 F803 ЗЕ8А MVI A,9AH F805 320380 STA W55+3 ;Инициализация КР580ВГ75 F808 2101C0 BEGIN: LXI H,VG75+1 F80B 3600 MVI M,B F00D 2В DCX H F80E 364D MVI M,4DH F010 361D MVI M,1DH F812 3699 MVI M,99H F814 3693 MVI M,93H ; Инициализация КР580BT57 F816 3E80 MVI A,80H P818 3208Е0 STA VT57+8 F818 2104E0 LXI H,VT57+4 F81E 36D0 MVI M,BD0H F82a 3636 MVI M,36H F822 23 INX H F923 3623 MVI M,23H f825 3649 MVI M,49H ; Старт ПДП F827 3EA4 MVI A,0A4H F829 3208E0 STA VT57+8 ; Заполнение экранной области ОЗУ F82С 210036 LXI Н,3600Н F82F 7D LABEL1: MOV A,L F850 E67F ANI 7FH F832 77 MOV M,A F833 23 INX H F834 7C MOV A,H F835 FE40 CPI 40Н FB37 C22AF8 JNZ LABEL1 ; Старт отображений F83A 3E27 MVI A,27H F83C 3201C0 STA VG75+1 ; Проверка работы клавиатуры F83F 210080 LXI H,W55 F842 367F MVI M,7FH F844 7E LABEL2: MOV A,M F845 07 RLC F846 77 MOV M,A F847 3A0180 LABEL3: LDA VV55+1 F84A 3C INR A F84B C247F8 JNZ LABEL3 F84E C344F8 JMP LABEL2 F851 END

Таблица 2.

Сигналы в «Радио-86РК» при пошаговом выполнении отладочной программы.

| Команда | № Такта | Шина адреса | Шина данных | Сигналы управления | |||||||||||||||||||||||

| A15 | A14 | A13 | A12 | A10 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | RD | WR | V | XS | XS | XS | XS | ||

| -A11 | -A6 | [1] | [2] | D11 | D2 | D8 | D17 | D20 | |||||||||||||||||||

| JMP F803 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | ||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | ||

| MVI A,8A | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| STA 8003 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0` | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| LXI H,C001 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,00 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| DCX H | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | −0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,4D | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,1D | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,99 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,93 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| MVI A,80 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| STA E008 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| LXI H,E004 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,D0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,36 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | ||

| INX H | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,23 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1` | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| MVI M,49 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | ||

| MVI A,A4 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| STA E008 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | ||

- [1] — D4/3, D8/9, D14/5, D17/20, D20/5

- [2] — D2/2, D5/13, D8/10, D14/.36, D17/18, D20/36, D22-D29/

После подключения «пошагивателя» на выходе RDY тактового генератора должен установиться низкий уровень. На входах микропроцессора Ф1, Ф2, RES, RDY должны присутствовать те же сигналы, что и на одноименных выходах тактового генератора. На входах INT и HOLD микропроцессора должен установиться низкий уровень.

После нажатия кнопки «СБРОС» проверяют наличие кода 0С3Н на шине данных микропроцессора. При отсутствии кода на шине следует проверить наличие низкого уровня на входах CS и OE ПЗУ К573РФ5 (D17). При отсутствии сигнала ОЕ проверить цепь сигнала DBIN (D6 — лог. 1) — выход элемента D5.1 (лог. 0). При отсутствии сигнала CS проверить выход элемента D13.2 (лог. 0) выход 7 микросхемы D11 (лог. 1) и выход элемента D4.3 (лог. 0). При отсутствии кода 0С3Н на шине данных проверяют наличие низкого уровня на входах А0-А10 ПЗУ и высокого — на входах CS микросхем D2, D8, D14, D20 и на входах CAS микросхем D22-D29. Если уровни присутствуют, то неисправность вероятнее всего заключается в коротком замыкании или обрыве на шинах данных и адреса.

Далее дважды нажимают кнопку «ШАГ», проверяя каждый раз на шине данных наличие кодов 01ВН и 0F8H соответственно. При необходимости устраняют неисправности на линиях шин данных и адреса и проверяют работу «пошагивателя» просмотром изменения состояний младших разрядов шины адреса.

Затем проверяют работу триггера начального запуска (D13.2). Для этого подсоединяют щуп осциллографа к входу V дешифратора D11, нажимают кнопку «СБРОС» и убеждаются в наличии на этом входе низкого уровня. Затем трижды нажимают кнопку «ШАГ» — уровень должен измениться на высокий. Если после сброса низкий уровень отсутствует, проверяют цепь RES D1, вход D9.2, R D13.2, а при отсутствии (после трех шагов) высокого уровня на входе V(D11) — цепь А15, DBIN D6 (лог. 1), вход D10.1 (лог. 0), S D13.2.

Следующий этап — проверка наличия кода 03ЕН на шине данных после троекратного (от «СБРОСа») нажатия кнопки «ШАГ». При его отсутствии проверяют наличие низкого уровня на выходе 7 дешифратора D11, если уровень низкий — убеждаются в наличии высокого уровня на входах А0- А2 и V и низкого на выводах 4 и 5 микросхемы D11.

На входах А0-А10 микросхемы D17 при этом должен присутствовать код 0003Н, а на входах CS и ОЕ — низкий уровень.

Затем проверяют настройку порта обслуживания клавиатуры, для чего еще пять раз нажимают кнопку «ШАГ». После этого на входе CS (D20) должен установиться низкий уровень, если этого не произошло, проверяют цепь А0-А2 микросхемы D11 (001В), вывод 4 D11 (лог. 0). На входе WR микросхемы D20 должен появиться низкий уровень, если его нет — проверяют цепи сигнала WR (D6). Если и в этом случае низкий уровень отсутствует, следует убедиться в исправности микросхемы D2.

Отсутствие кода 08АН на входах D0-D7 микросхемы D20 говорит о возможных обрывах в линиях шины данных. Кнопку «ШАГ» нажимают еще раз и проверяют наличие высокого уровня на входах С5-С7 микросхемы D20 — возможные неисправности заключаются либо в микросхеме D20, либо отсутствии нагрузочных резисторов в блоке клавиатуры.

Далее приступают к проверке работы контроллера прямого доступа к памяти К580ИК57. Для этого необходимо вынуть из панели микросхему D8 и соединить между собой контакты 5 и 40. Если эта микросхема запаяна в плату, то необходимо аккуратно перерезать проводник, соединяющий выводы DRQ микросхемы D8 и DRQ2 микросхемы D2. На вывод DRQ2 микросхемы D2 подают напряжение +5 В. Теперь нажимают кнопку «СБРОС», а затем кнопку «ШАГ» до седьмого появления сигнала низкого уровня на входе IOWR микросхемы D2. При этом на входе IOWR микросхемы D2 должен появиться такой же уровень.

Вслед за этим проверяют наличие сигнала Ф2ТTL на входе CLK микросхемы D2, и затем, нажав кнопку «СБРОС», нажимают кнопку «ШАГ» до двенадцатого появления низкого уровня на входе IOWR микросхемы D2. После следующего нажатия на эту кнопку контроллер ПДП D2 оказывается настроенным и начинает выполнять циклы ПДП, то есть формировать управляющие сигналы и адреса. В этом можно убедиться, проверив наличие сигнала с частотой 420 кГц и скважностью около 5 на входе ASTB микросхемы D2. На вход WR контроллера КР580ВГ75 должны поступать от контроллера ПДП отрицательные периодические импульсы той же частоты. Если этих сигналов нет, необходимо проверить наличие высокого уровня на выходе DRQ и входах HLDA, DRQ2, RDY микросхемы D2, а также проверить шину данных и линии А0-А3 шины адреса.

Затем отключают «пошагиватель» от входа RDYI N тактового генератора. При этом после нажатия на «СБРОС» контроллер ПДП входит в режим прямого доступа автоматически. Для проверки работы контроллера просматривают сигналы ни линии А0-А10 шины адреса микропроцессора. На линии А0 должны присутствовать сигналы частотой 210кГц и скважностью 2. На каждой последующей линии шины адреса сигналы будут следовать с частотой, вдвое меньшей, чем на предыдущей (A1-105кГц, А2- 52кГц, A11- 50 Гц). На линиях А14-А15 должны присутствовать соответственно низкий, а на А12 и А13- высокий уровень. Сигналы на линиях А8-А15 могут иметь положительные выбросы длительностью менее 50 нс. Если на линиях А8-А10 наблюдаются иные сигналы, следует проверить работу микросхемы D7.

Далее проверяют работу сдвигового регистра D16. На его выходах 01-Q3 при работе контроллера ПДП наблюдаются отрицательные импульсы, причем длительность импульсов на выходе Q3 должна быть на 62нс. меньше, чем на Q2, и на 125нс. меньше, чем на Q1. В противном случае проверяют наличие сигналов на входах микросхемы D16.

Для дальнейшей наладки РК необходимо убедиться в отсутствии коротких замыканий и обрывов на мультиплексированной шине адресов памяти и проверить работу мультиплексоров адреса, для чего на максимально удаленной от мультиплексоров D18, D19 микросхеме ОЗУ (D29) просмотреть сигналы на входах мультиплексированных адресов ОЗУ А0-А6. Изменение логических уровней должно происходить с частотой, большей частоты обращения (420 кГц). Если это не так, возможен обрыв мультиплексированной адресной линии или неисправность мультиплексора. Для их проверки следует просмотреть сигналы на входах V и удостовериться в наличии низкого уровня на входах CS. Необходимо также проверить идентичность сигналов на входах А0-A3, В0-В3 мультиплексоров и соответствующих сигналов на шине адреса микропроцессора. При наблюдении на экране осциллографа сигналов на мультиплексированных адресных линиях должно присутствовать только два уровня. Наличие каких-либо промежуточных уровней свидетельствует о коротком замыкании на мультиплексированной шине адресов ОЗУ.

Далее следует убедиться, что сигналы на входах RAS и CAS микросхем ОЗУ эквивалентны сигналам на выходах Q1 и Q3 микросхемы D16 соответственно, а также в присутствии на входе WE этих микросхем высокого уровня.

Работоспособность микросхем памяти можно проверить, наблюдая (осциллографом) сигналы на их выходах.

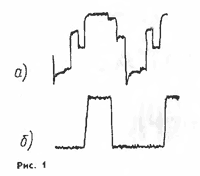

Сигналы на двух старших линиях шины данных (рис, 1) отличаются от остальных (рис. 1, а). Если это не так, значит неисправны соответствующие микросхемы памяти.

Для проверки работы контроллера ЭЛТ КР580ВГ75 необходимо вновь подключить «пошагиватель» к входу RDYIN тактового генератора и вставить в панель микросхему D8 или восстановить разорванную связь. Наличие импульсов с частотой 1,3 МГц (16/12) и скважностью 2 проверяют на входе CCLK микросхемы D8, если импульсов нет, то убеждаются в наличии сигналов в цепи D3/14 — D3/12 — D3/1 — D3/8. Затем один раз нажимают кнопку «СБРОС» и 14 раз кнопку «ШАГ», после чего на входе CS контроллера D8 должен появиться низкий уровень. Следует также проверить наличие низкого уровня на входе WR микросхемы D8, а в случае его отсутствия убедиться в наличии такого же уровня на выводе 1 элемента D4.1.

Далее кнопку «ШАГ» нажимают до появления пятого (после сброса) низкого уровня на входе CS микросхемы D8. После следующего «ШАГа» проверяют наличие сигналов с периодами 64 мкс и 20мс на выходах HRTC и VRTC контроллера ЭЛТ соответственно. В случае их отсутствия следует удостовериться в целостности линий шины данных и линии А0 шины адресов между процессором и контроллером ЭЛТ и наличии высокого уровня на входе RD микросхемы D8.

Чтобы убедиться в правильности взаимодействия контроллеров ЭЛТ, ПДП и ОЗУ «пошагиватель» необходимо отключить. Нажав кнопку «СБРОС», проверяют наличие сигнала с периодом 64 мкс на выходе VSP контроллера D8. Его присутствие свидетельствует о исправности проверяемых элементов компьютера. В случае отсутствия сигнала VSP возможна неисправность микросхемы КР580ВГ75 контроллера ЭЛТ или микросхемы динамического ОЗУ К565РУЗ (D27).

Далее, подключив к компьютеру телевизор и нажав на кнопку «СБРОС», ожидают появления на экране всех символов, причем символы должны отображаться на всем поле экрана в порядке возрастания их кодов. Нарушение этого порядка свидетельствует о неисправности соответствующей микросхемы динамической памяти К565РУ3. Если какие-либо символы отображаются на экране в искаженном виде, то надо проверить ПЗУ знакогенератора. При отсутствии символов на экране необходимо проверить наличие сигналов низкого уровня на выходах D0-D5 микросхемы D12. Если их нет, проверяют наличие сигнала VSP на входе CS микросхемы D12, низкого уровня на входе PGM и периодических сигналов на входах А0-А9. Наличие всех сигналов свидетельствует о неисправности ПЗУ знакогенератора или обрывах в цепях резисторов R6-R12.

Символы могут не отображаться также при отсутствии высокого уровня на входах S1 и R0, сигналов частотой 8 МГц на входе С и частотой 1,3 МГц на входе S1 (на этом входе скважность сигнала равна 6) сдвигового регистра D15. В этих случаях уровень напряжения на выходе Q5 сдвигового регистра неизменен. Если на этом выходе имеется изменяющийся сигнал, то неисправность надо искать в узле формирования видеосигнала (элементы D5.2, D9.3, D9.4, V2, R15 — R19, С3, С4).

Затем проверяют наличие сигналов опроса клавиатуры на выходах А0-А7 (D20). При их отсутствии причина может крыться в неисправности шины данных и двух младших разрядах шины адреса между портом D20 и микропроцессором, а также отсутствии прохождения сигнала «СБРОС» на вход RES (D20).

Далее убеждаются, что при нажатии на какую-либо клавишу клавиатуры на линиях порта А и В, в пересечении которых находится ее замкнутый контакт, устанавливается низкий уровень. Символ на экран не выводится.

Теперь можно установить в компьютер ПЗУ с управляющей программой МОНИТОР. Прежде всего, надо протестировать ОЗУ, для чего дважды выполнить следующие директивы, подставляя вместо ** сначала 00, а потом FF:

->F0,35FF, ** <ВК> ->C0,1AFF,1В00<ВК>

Выявленные ошибки — несовпадение записанной информации в областях ОЗУ — свидетельствуют о неисправности соответствующих микросхем памяти. Такое тестирование памяти, конечно, не позволяет быть полностью уверенным в работоспособности ОЗУ, но гарантирует от явных неисправностей.

Работу магнитофонного интерфейса проверяют, выполняя следующие директивы МОНИТОРа:

->F0,1FFF,00<BK> ->O0,1FFF<BK>

При этом на выходе для записи на магнитофон должны появиться импульсы частотой 600 Гц, скважностью, близкой к 2, и амплитудой около 2,5 В. Если сигнал отсутствует, проверяют работу соответствующей микросхемы РК.

Далее соединяют через конденсатор емкостью 0,05 мкФ вход, и выход компьютера для записи и считывания с магнитофона и выполняют те же директивы. На входе С4 порта D20 должен присутствовать такой же сигнал, что и в первом случае, но с амплитудой около 4 В. Если он отсутствует или скважность сигнала не лежит в пределах 1,9…2,1, следует искать неисправность в схеме чтения с магнитофона. В заключение производят аналогичную проверку, выполняя директивы:

->F0,1FFF,55<BK> ->O0,1FFF<BK>

Частота сигнала при этом должна быть в 2 раза меньше.

Д. ГОРШКОВ, Г. ЗЕЛЕНКО. Ю. ОЗЕРОВ, г. Москва