588ВГ1: различия между версиями

Nzeemin (обсуждение | вклад) Нет описания правки |

Nzeemin (обсуждение | вклад) |

||

| Строка 253: | Строка 253: | ||

== Описание (Шахнов) == | == Описание (Шахнов) == | ||

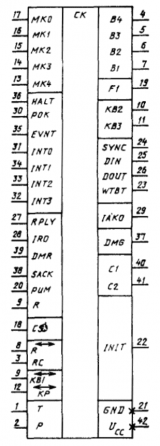

[[Файл:Shahnov-8-13.png|thumb|160px|Рис. 8.13. Условное графическое обозначение К588ВГ1]] | |||

Микросхема К588ВГ1 — системный контроллер (СК), предназначен для применения совместно с микросхемами К588ВУ2, К588ВС2 в процессоре 16-разрядной микро-ЭВМ. | Микросхема К588ВГ1 — системный контроллер (СК), предназначен для применения совместно с микросхемами К588ВУ2, К588ВС2 в процессоре 16-разрядной микро-ЭВМ. | ||

Версия от 17:35, 22 октября 2022

| Этот документ создан для Emuverse и распространяется на условиях лицензии CC-BY-SA-3.0. |

К588ВГ1 — микросхема системного контроллера из микропроцессорного комплекта 588.

Назначение выводов

Описание (Гришин)

Большая интегральная схема системного контроллера (БИС СК.) предназначена для согласования и сопряжения процессора на базе микросхем серии К588 (КР588) с каналом типа Q-шина. Назначение выводов БИС СК дано в табл. 6.10. На рис. 6.10 и 6.11 изображены соответственно условное обозначение и структурная схема БИС СК.

В состав структурной схемы БИС СК входят следующие функциональные узлы: блок прерываний БП, дешифратор микрокоманд ДШМ, блок управления обменом данных БУО, блок управления прямым доступом к памяти БУНД, блок правления магистральными приемопередатчиками БУПП, блок синхронизации БСЗ.

Следует отметить, что линии управления обменом ЛУО включают следующие сигналы обмена (см. рис. 6.11): ОБМ, ДЧТ, ДЗП, ПЗП, ОТВ, ЗПР, ПРР и ПВС.

Линии передачи управления ЛПУ включают сигналы ЗМ, РЗМ и ПЗ (см. рис. 6.11).

БИС СК предназначена для связи внутреннего интерфейса процессора, построенного на базе микросхем серии К588 (КР588), с внешним стандартным интерфейсом канала Q-шина.

Внутренний интерфейс процессора содержит сигналы, обеспечивающие работу процессора, состоящего из магистральных приемопередатчиков, управляющей памяти и арифметического устройства. Это сигналы квитирования БИС АУ и БИС УП, 16-разрядная информационная магистраль, 4-разрядная магистраль кода прерывания, сигналы управления магистральными приемопередатчиками. Сигналы квитирования КВ1 … КВЗ и КП обеспечивают передачу информации по 16-разрядной магистрали. Информация может включать команду, данные, адрес, вектор прерывания. Магистраль кода прерывания ПРЗ … ПРО служит для сообщения в УП о том, какое прерывание в данный момент обслуживается.

Сигналы управления приемопередатчиками С1 и С2 предназначены для организации двунаправленного обмена информацией через МПП.

- Рис. 6.10. Условное графическое обозначение микросхемы К588ВГ1

- Рис. 6.11. Структурная схема микросхемы К588ВГ1

Внешний интерфейс процессора содержит сигналы, обеспечивающие работу всех устройств канала. Это информационные шины, шины управления вводом-выводом, шины прерываний и шины прямого доступа к памяти. Сигналы на шинах ввода-вывода ОБМ, ДЧТ, ДЗП, ПЗП, ОБМ обеспечивают передачу по двунаправленной шине данных Д15 … ДО команд, адресов, данных и векторов прерываний.

Шины и сигналы прерываний ЗПРЗ…ЗПР0, ОСТ, АИП, ЗПР, ПРР, ЛВС служат для приема запросов на прерывание и для сброса прерываний от внешних устройств.

Шины прямого доступа ЗМ, РЗМ, ПЗ служат для приема запросов на прямой доступ к памяти и сброса этих запросов.

Сигнал УСТ служит для приведения системы в исходное состояние, КОШ — вывод для подключения внешней времязадающей цепи для формирования длительности сигналов УСТ, ДЧТ или ДЗП.

БИС СК управляется микрокомандно. В табл. 6.11 приведена система микрокоманд БИС СК. Код микрокоманды поступает на входы МК4 … МКО.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | Регистр состояния | T | T | Вход |

| 2 | P | P | ||

| 3 | Подключение времязадающей цепи | — | КОШ | |

| 4 | Шина прерывания | 3 | ПР3 | Выход |

| 5 | 2 | ПР2 | ||

| 6 | 1 | ПР1 | ||

| 7 | 0 | ПР0 | ||

| 8 | Начальная установка | — | R | |

| 9 | Квитирование выдачи | 1 | КВ1 | Вход-выход |

| 10 | 2 | КВ2 | Выход | |

| 11 | 3 | КВ3 | ||

| 12 | Квитирование приема | — | КП | Вход-выход |

| 13 | Шина микрокоманд | 4 | МК4 | Вход |

| 14 | 3 | МК3 | ||

| 15 | 2 | МК2 | ||

| 16 | 1 | МК1 | ||

| 17 | 0 | МК0 | ||

| 18 | Строб микрокоманды | — | ВК | |

| 19 | Квитирование приема микрокоманды | — | Ф1 | Выход |

| 20 | Начальный пуск | — | НП | Вход |

| 21 | Общий | — | GND | — |

| 22 | Сброс канала | — | УСТ | Выход |

| 23 | Линии управления обменом | 3 | ЛУО3 | |

| 24 | 0 | ЛУО0 | ||

| 25 | 1 | ЛУО1 | ||

| 26 | 2 | ЛУО2 | ||

| 27 | 4 | ЛУО4 | ||

| 28 | 5 | ЛУО5 | Вход | |

| 29 | 6 | ЛУО6 | Выход | |

| 30 | Внешний сигнал прерывания | — | АИП | Вход |

| 31 | Запрос прерывания с фиксированными векторами | 0 | ЗПР0 | |

| 32 | 3 | ЗПР3 | ||

| 33 | 2 | ЗПР2 | ||

| 34 | 1 | ЗПР1 | ||

| 35 | Линии управления обменом | 7 | ЛУО7 | |

| 36 | Внешний сигнал прерывания | — | ОСТ | |

| 37 | Линии передачи управления | 1 | ЛПУ1 | Выход |

| 38 | 2 | ЛПУ2 | Вход | |

| 39 | 0 | ЛПУ0 | ||

| 40 | Управление приемопередатчиком | 1 | С1 | Выход |

| 41 | 2 | С2 | ||

| 42 | Напряжение питания | — | Uco | — |

| Восьмерич- ный код |

Обозначение | Назначение |

|---|---|---|

| 00 | INIT | Инициализация работы БИС СК |

| 01 | LPSW | Загрузка слова состояния программы |

| 02 | DATIV | Ввод вектора прерывания |

| 03 | WAIT | Ожидание |

| 04 | IE | Разрешение прерывания |

| 05 | ID | Запрет прерывания |

| 10 | DATI | Ввод слова |

| 11 | DATIK | Ввод команды |

| 12 | DATO | Вывод слова |

| 13 | DATOB | Вывод байта |

| 14 | DATIO | Ввод-вывод слова |

| 15 | DATIOB | Ввод-вывод байта |

| 20 | RTO | Сброс прерывания INTO |

| 21 | NH | Запрет прерывания HALT |

| 22 | RT1 | Сброс прерывания INT1 |

| 23 | RT2 | Сброс прерывания INT2 |

| 24 | RT3 | Сброс прерывания INT3 |

| 25 | RH | Сброс прерывания HALT |

| 26 | RTM | Сброс триггера маски |

| 27 | RES | Начальная установка |

| 30 | RTE | Сброс триггера ошибки |

| 31 | RTP | Сброс триггера РОК |

| 32 | CTO | Очистка триггера ТО |

| 33 | NTI | Запрет прерывания |

| 34 | REV | Сброс триггера |

| 37 | NOP | Нет операции |

Рассмотрим выполнение трех микрокоманд, управляющих процессами ввода и вывода информации.

Микрокоманда ввода команды DАТІК (рис. 6.12) выполняется следующим образом.

На вывод КВ1 подается сигнал из БИС АУ о том, что на магистрали данных находится адрес команды. По этому сигналу БИС СК устанавливает сигналы разрешения обмена ОБМ = «0» и чтения данных ДЧТ = «0» для ОЗУ, а также разрешает БИС АУ снять с магистрали данных адрес команды, выдав сигнал КП = «О».

После снятия адреса команды БИС АУ выдает сигнал на вывод КВ1 = «1», на что БИС СК отвечает сигналом КП = «1».

Затем на вывод ОСТ подается сигнал «0», свидетельствующий о том, что на магистрали данных находится команда и БИС СК разрешает УП принять команду. Кроме этого, при отсутствии запросов на прерывание БИС СК выдает сигналы КВ2 = КВЗ = «0». Если к данному моменту запрос на прерывание поступит, то БИС СК вырабатывает сигнал КВЗ = «0».

После приема команды БИС УП отвечает сигналом КП = «0», по которому БИС СК вырабатывает сигналы КВ2 — КВЗ = «1», а также сигнал ДЧТ — «1».

После снятия сигнала ОСТ (ОСТ = «1») БИС СК снимает сигнал ОБМ (ОБМ = «1»).

Выполнение микрокоманды ввода данных ОАТІ (рис. 6.13) начинается с подачи из БИС А У на БИС СК сигнала КВ1 = «0», который свидетельствует о том, что адрес данных находится на магистрали.

По этому сигналу БИС СК устанавливает сигналы ОБМ = «0», ДЧТ = «0» (для ОЗУ или ВУ). Затем, после задержки относительно сигнала ОБМ, БИС СК устанавливает сигнал КП = «0», который разрешает снять адрес с магистрали данных. После этого АУ вырабатывает сигнал КВ1 = «1», по которому БИС СК устанавливает сигнал КП = «1».

- Рис. 6.12. Временная диаграмма выполнения микрокоманды DАТІК

- Рис. 6.13. Временная диаграмма выполнения микрокоманды DАТІ

На БИС СК подается сигнал ОСТ = «0» (данные находятся на магистрали). По этому сигналу БИС СК устанавливает сигнал КВ1 = «0», разрешая БИС АУ принять данные. После окончания приема данных БИС АУ вырабатывает сигнал КП = «0». Вслед за этим БИС СК сбрасывает сигналы КВ1 и ДЧТ в состояние «1». Получив сигнал ОСТ = «1», БИС СК вырабатывает сигнал ОБМ = «1».

| Двоичный код |

Мнемокод | Содержание прерываний |

|---|---|---|

| 1 0 1 0 | W (DBE) | Начальный пуск (двойная ошибка канала) |

| 1 1 1 0 | T (TERR0) | Прерывание по T-разряду |

| 1 1 1 1 | POK (TERR1) | Прерывание по сбою питания (ошибка канала) |

| 0 1 1 1 | HALT (TERR2) | Прерывание по входу ОСТ (ошибка канала) |

| 0 1 0 1 | INT0 | Запрос прерывания 0 от ВУ |

| 0 1 0 0 | INT1 | То же . . . 1 |

| 0 1 1 0 | INT2 | » . . . . . 2 |

| 0 0 1 0 | INT3 | » . . . . . 3 |

| 0 0 0 1 | IRQ | Запрос прерывания от ВУ с нефиксированным вводимым адресом-вектором |

| 0 0 0 0 | Нет прерывания | Нет прерывания |

Выполнение микрокоманды вывода данных ОАТО (рис. 6.14) начинается с подачи из БИС АУ на БИС СК сигнала КВ1 = «0», свидетельствующего о том, что на магистрали находится адрес данных. Поэтому сигналу БИС СК станавливает сигналы ОБМ = ПЗП = «0» (для ОЗУ или ВУ). Затем с некоторой задержкой относительно сигнала ОБМ БИС СК устанавливает сигнал КП = «0». Последний разрешает БИС АУ снять адрес данных, после чего БИС АУ вырабатывает сигнал КВ1 = «1». По этому сигналу БИС СК отвечает сигналами ПЗП = КП = «1».

АУ выставляет на магистраль данные, сигнализируя об этом сигналом КВ1 = «0», по которому БИС СК устанавливает сигнал ДЗП = «0» (для ОЗУ или ВУ). После того, как данные запишутся в ОЗУ (ВУ) на БИС СК подается сигнал ОСТ = «0». По этому сигналу БИС СК вырабатывает сигналы ДЗП = «1» и КП = «0». Получив сигнал КП = «0», БИС АУ снимает данные с магистрали и устанавливает сигнал КВ1 = «1», по которому БИС СК формирует сигнал КП = «1». По сигналу сигнал ОБМ = «1».

- Рис. 6.14. Временная диаграмма выполнения микрокоманды DATO

В табл. 6.12 приведена расшифровка кодов, вырабатываемых БИС СК на выводах ПРЗ … ПРО.

Электрические параметры БИС СК приведены в табл. 6.13.

При разработке схемы с использованием БИС СК подключение времязадающей РС-цепочки к выводу КОШ осуществляется следующим образом: резистор R — между питанием и выводом КОШ; конденсатор С — между выводом КОШ и «минусом» источника питания. Значения резистора и конденсатора подбираются из условия обеспечения нужной длительности сигналов ДЧТ, ДЗП, до сигнала ОТВ.

Описание (Шахнов)

Микросхема К588ВГ1 — системный контроллер (СК), предназначен для применения совместно с микросхемами К588ВУ2, К588ВС2 в процессоре 16-разрядной микро-ЭВМ.

Микросхема является микропрограммно управляемым асинхронным модулем, обеспечивающим взаимосвязь микросхем процессора на базе микропроцессорного комплекта серии К588 и организующим интерфейс процессора. Она выполняет следующие функции: ввод, вывод 16-разрядного слова или байта; обслуживание внешних и внутренних прерываний; управление прямым доступом к памяти; управление двунаправленными премопередатчиками.

Условное графическое обозначение микросхемы приведено на рис. 8.13, назначение выыводов — в табл. 8.17, структурная схема показана на рис. 8.14.

Микросхема включает в себя следующие основные блоки: блок прерываний (БП); блок ввода/вывода (БВ/ВВ); блок внутреннего управления (БВУ); блок прямого доступа к памяти (БПДП); блок управления приемопередатчиками (БУП).

Блок прерываний предназначен для приема запросов на обслуживание прерывания и выдачи кода прерываний в соответствии с табл. 8.18.

Блок ввода/вывода предназначен для формирования на шинах ввода/вывода стандартной временной последовательности; БВУ — для формирования в микросхеме внутренних синхросигналов; БПДП — для приема запросов на захват канала при прямом доступе к памяти; БУП — для включения и выключения канальных приемопередатчиков.

Структурная схема соединения микросхем К588ВГ1, К588ВУ2, К588ВС2, К588ВА1 в составе процессора приведена на рис. 8.15.

Системный контроллер связывает внутренний интерфейс процессора с внешним интерфейсом.

Внутренний интерфейс содержит линии, обеспечивающие совместную работу в процессоре: блока микросхем управляющей памяти (УП); арифметического устройства (АУ); блока микросхем магистрального приемопередатчика (МПП).

Внешний интерфейс процессора содержит сигналы, обеспечивающие работу устройств канала. Это шины ввода/вывода, прерываний и прямого доступа к памяти.

Сигналы на шинах ввода/вывода SYNC, DIN, DOUT, WTBT, PRLY обеспечивают управление передачей по 16-разрядной двунаправленной шине DA0-DA15 команд, адресов, данных и векторов.

Шины прерываний INT0, INT1, INT2, INT3, HALT, POK, IRQ, IAKO, EVNT служат для приема запросов на прерывания и сброса прерываний от внешних устройств.

Шины прямого доступа к памяти DMR, DMG, SACK служат для управления предоставлением прямого доступа к памяти.

Шина инициализации INIT служит для приведения внешних устройств в исходное состояние.

Система микрокоманд приведена в табл. 8.19, временные диаграммы выполнения микрокоманд DATI и DATO показаны на рис. 8.16.

Основные параметры микросхемы приведены в табл. 8.20.

Литература

- [Гришин] Г. Г. Гришин, А. А. Мошков, О. В. Ольшанский, Ю. А. Овечкин. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. Л.: Судостроение, 1987. Глава 6. МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ СЕРИИ К588 (КР588)

- [Шахнов] Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник. В 2 т. / Под ред. В. А. Шахнова. — М.: Радио и связь, 1988. — T. 1. — 368 с.: ил.

- [Хвощ] Хвощ С. Т. Микропроцессоры и микроэвм в системах автоматического управления.